是德科技

ADS 克服信号和电源完整性挑战的

10 种方法

技术概述

Unlocking Measurement Insights

Keysight EEsof EDA 的先进设计系统 (ADS) 软件是全球闻名的电子设计自动化软件, 是射频、微波和高速数字应用的理想选择。为了提高效率, ADS 采用了一系列新技术, 其中包括两个电磁 (EM) 软件解决方案, 专门用于帮助信号和电源完整性工程师提高 PCB 设计中的高速链路性能。以下列出了 ADS 帮助工程师克服信号和电源完整性挑战的 10 种方法。

1. ADS 为您的 SI EM 表征提供出色的速度和准确性.....第 2 页

2. ADS 简化部件 S 参数文件的使用.....第 4 页

3. ADS 提供先进的通道仿真器技术.....第 6 页

4. ADS 立身于技术 (如 PAM-4) 潮头 .....第 9 页

5. ADS 加速 DDR4 仿真方法 .....第 12 页

6. ADS 将电源交到设计人员 (PI 分析) 手中 .....第 15 页

7. ADS 可实现平坦的 PDN 阻抗响应 .....第 18 页

8. ADS 提供电热仿真 .....第 21 页

9. ADS 有一个互连工具箱 (Via Designer 和 CILD) .....第 22 页

10. ADS 传递是德科技理念:

人力资源、硬件和软件资源的结合, 开启测量新视野.....第 23 页

## 1. ADS 为您的 SI EM 表征提供出色的速度和准确性

在精确表征高速通道的损耗和耦合时, 通常会使用电磁 (EM) 技术。随着数据速率提升, 我们面临的一个主要困境是选择使用哪种 EM 技术。全波通用 EM 仿真工具可在高频下提供所需的精度。用于 SI 分析的 3D-EM 技术的限制因素是 PCB 设计的规模和复杂性。高密度电路板需要花大量时间去手动简化版图, 根据所需仿真的信号网络进行切板, 并在实际的时间内 (通常要很多小时) 优化网格得到准确的仿真结果。设计人员一次只能验证电路板的一小部分。

相比之下, 混合仿真器则要快得多, 并且可以覆盖电路板上更大的网络范围。然而, 仿真是否能够与测量很好地关联, 这个问题始终存在。此外, 使用简化方法还让您错过了哪些 EM 效应?

ADS 推出了两种 EM 分析解决方案 — SIPro 和 PIPro, 它们专门为克服这些挑战而设计。SIPro 侧重于对大型、复杂的高速 PCB 上的高速链路进行 SI EM 分析, 而 PIPro 则侧重于对配电网 (PDN) 进行 PI EM 分析, 包括直流 IR 压降分析、交流 PDN 阻抗分析和电源面共振分析。

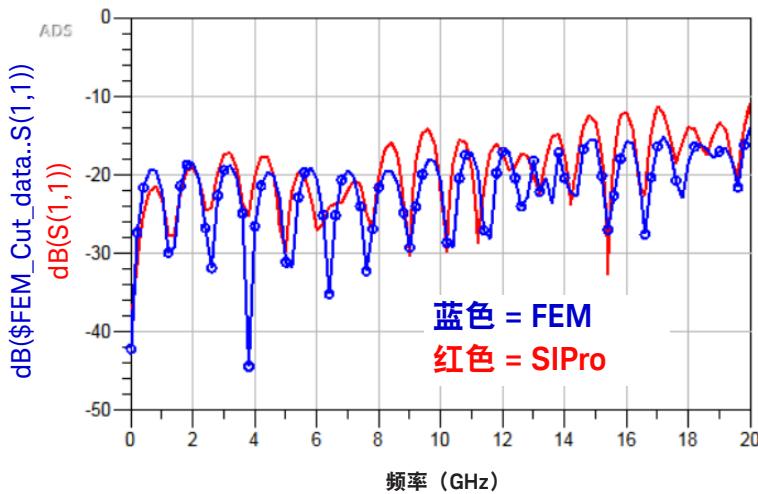

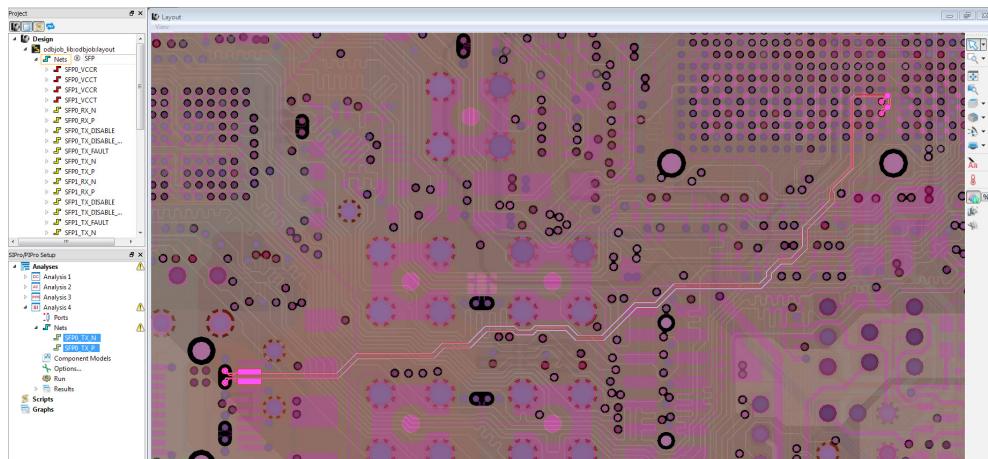

尤其是, SIPro 采用了复合 EM 技术, 提供比通用 EM 解决方案容量更高的纯 EM 分析。它可以捕获所有相关的 EM 效应, 如过孔之间的耦合、过孔到微带转换以及信号到地/电源面耦合。SIPro 和 PIPro EM 仿真器套件都提供了网络驱动的用户界面, 设计人员可以在这个界面上快速选择他们想要仿真的网络, 以及电源面和接地面及元器件, 并且无需花费时间或精力在仿真之前手动编辑或操作版图对象。端口也可以自动设置。利用这一流程, 设计人员只需不超过 20 次点击, 就能迅速完成从版图到获得仿真结果的过程 (图 1)。

## S11

SIPro: 1GB, 6 秒/频率点

全波 3D-EM: 8 GB, 12 分钟/频率点

图 1. SIPro 得出的结果其准确性接近全波 3D-EM 解决方案, 但花费的时间只有后者的一小半。

完成 EM 仿真后, 设计人员可以快速绘制 S 参数 (单端和混合模式)、TDR/TDT 和串扰的图形。这样, 他们就能快速评测 EM 模型是否经过充分表征, 以及通道是否正常。只需单击一次, 即可利用自动生成原理图功能将 EM 模型反向注释为 ADS 原理图, 使其通过一个简单的流程便能随时用于瞬态和通道仿真。凭借这些功能, SIPro 可为当今的设计人员提供他们所需的速度和准确性, 从现更高效的工作流程。

## 2. ADS 简化部件 S 参数文件的使用

设想您刚刚为自己正在考虑的一个部件（如用于背板的高速连接器）下载了 S 参数文件。该部件有很多端口，因此您首先想要检查数据的质量，然后用它进行仿真。您如何在原理图中连接它？哪些端口要配对？

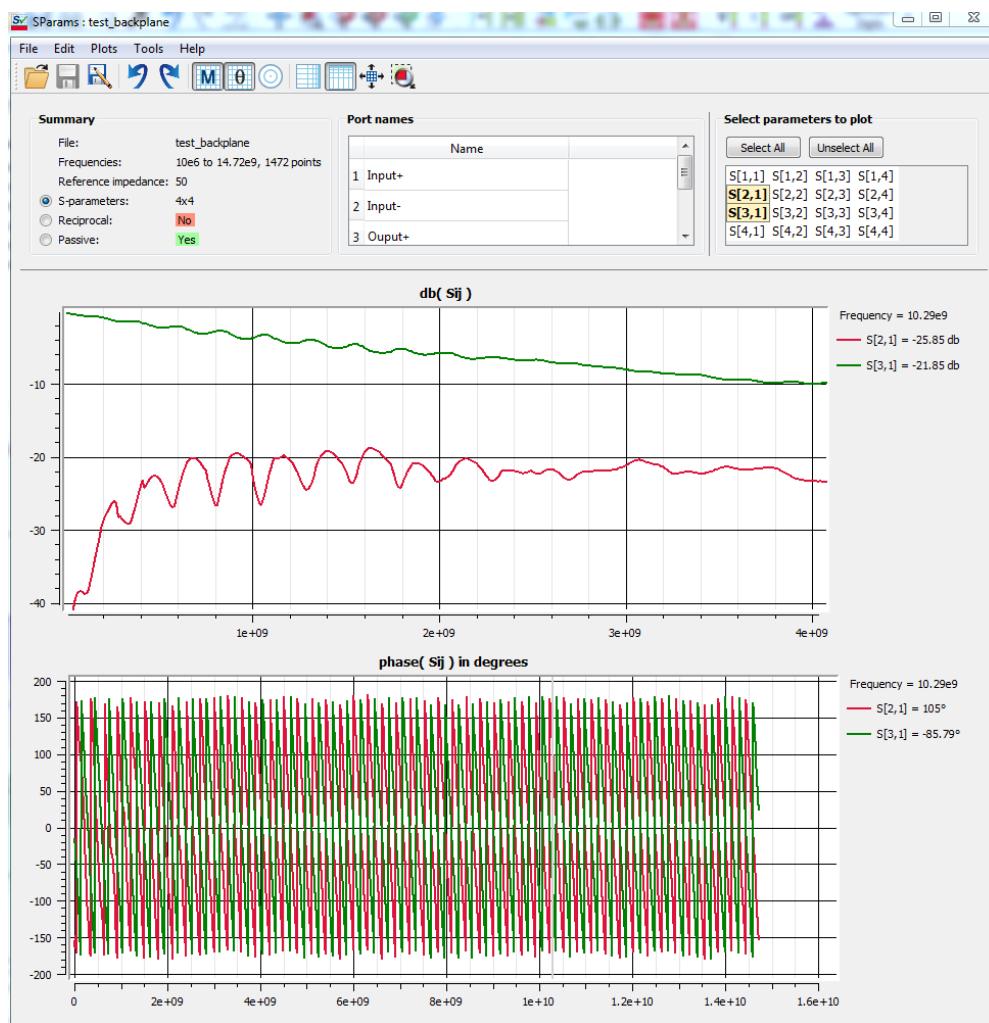

通常的做法可能是在文本编辑器中打开数据。但是，有了 ADS 的 S 参数检查器之后，设计人员现在可以轻松查看任何 S 参数文件的内容，而无需设置 S 参数测试台仿真。这使设计人员可以直接绘制他们希望看到的各种关系，并能显示每个引脚对应的端口名称。它还告诉设计人员该文件是无源的还是互易的，以及文件中的数据点数量和覆盖的频率范围。设计人员甚至可以使用 S 参数检查器来重命名端口、对端口进行重新排序和减少端口的数量，以便他们保存一个更有用的新 S 参数文件（图 2）。

图 2. 使用 S 参数检查器，设计工程师可以轻松重命名端口、对端口进行重新排序和减少端口的数量。

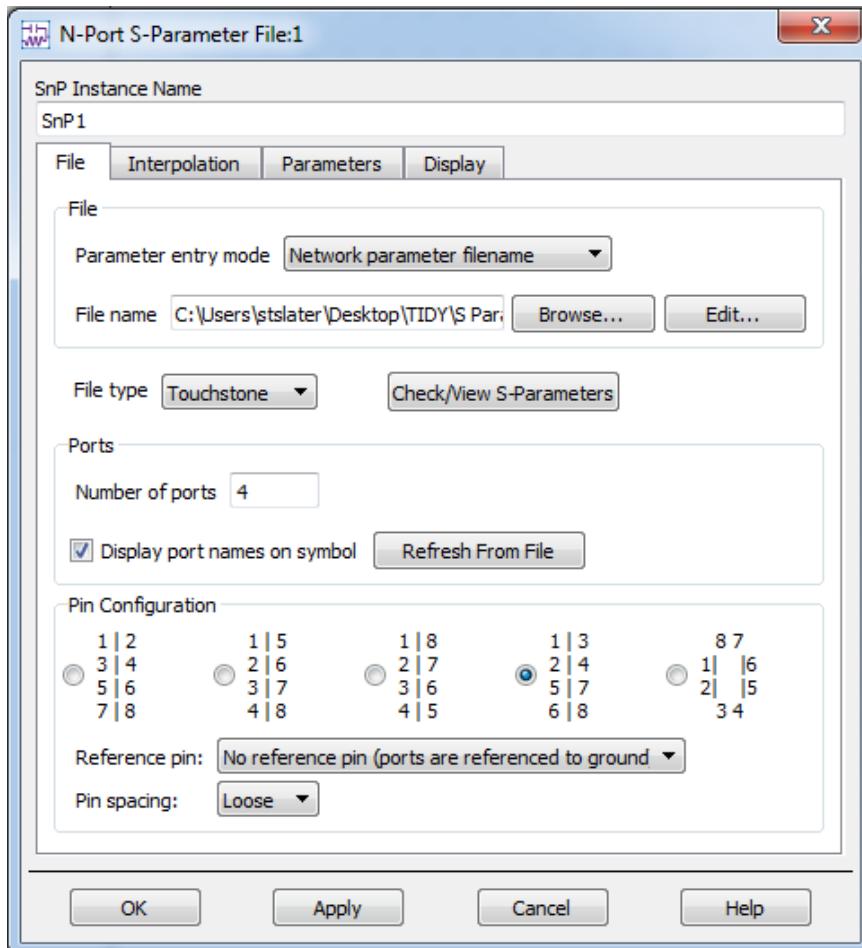

除了 S 参数检查器之外，最近的更新也让使用 S 参数文件进行 ADS 仿真变得更加容易。新的 SnP 组件将文件中的端口名称直接读取到符号上（图 3）。设计人员可以自由选择引脚的方向，以便所有输入都位于一侧，所有输出都位于另一侧。这样做的结果是可以避免电线的交叉。在此之后，设计人员要做的就是查看、编辑、放置、仿真、绘图和完成等操作（图 4）。

图 3. ADS 的 SnP 组件将文件中的端口名称直接读取到符号上，并允许您选择引脚方向。

图 4. 使用 S 参数检查器和 SnP 组件，下载和使用部件的 S 参数文件就剩下查看、编辑、放置、仿真、绘图和完成等操作。

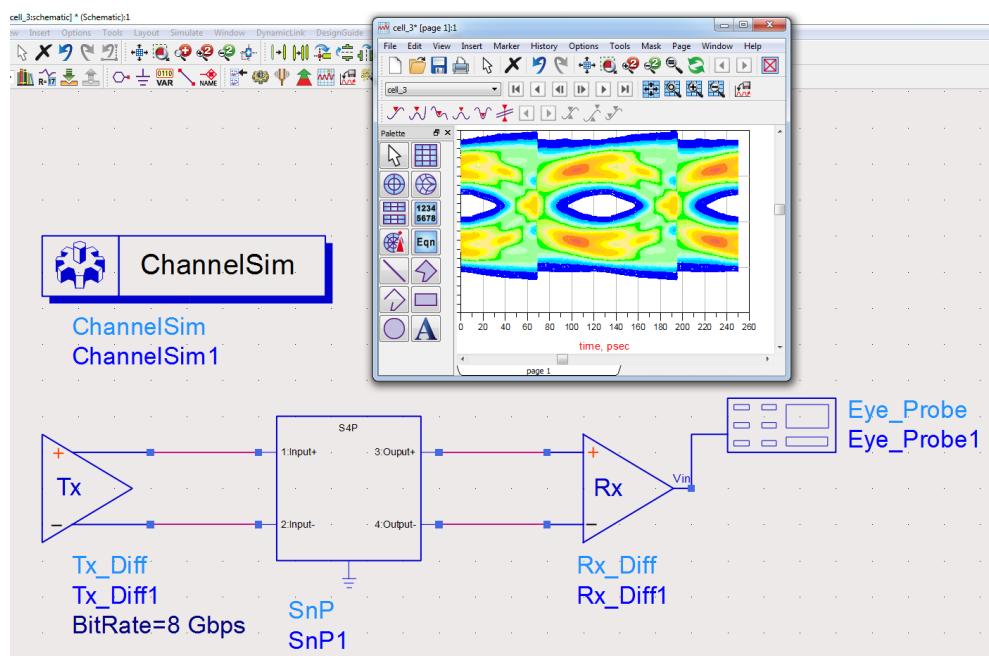

### 3. ADS 提供先进的通道仿真器技术

艰巨的技术挑战催生了突破性的新技术。对于 ADS 的通道仿真功能来说，情况确实如此。由于瞬态仿真（SPICE）无法满足模板裕量测量的需求，达不到非常低的比特误码率（BER），为了满足高速链路设计的需要，通道仿真应运而生。

在通道仿真之前，瞬态仿真仍是仿真高速链路设计的主要方法。然而，设计人员要克服困难重重的技术挑战：当误码率为  $1e-9$ 、 $1e-12$  或  $1e-16$  时，我的裕量如何？这些问题超出了瞬态仿真的能力范围，因为所需的时间步骤数量超出了实际采用的方法极限。通过通道仿真计算 BER 曲线是解决这一挑战的方法之一。

ADS 在通道仿真方面的技术优势始于 Fangyi Rao 博士在 2006 年获得的专利技术 — 在带宽有限的频域模型中纠正无源性，同时确保因果关系。Rao 博士的工作确保 ADS 成为在一个原理图中处理 S 参数模型与电路模型组合级联的更精准解决方案。在这项专利发布之后，通道仿真继续快步创新：

- 2009 年，逐位通道仿真发布。

- 2010 年，统计通道仿真发布。

- 2011 年，引入 IBIS-AMI 对通道仿真的支持。

- 2012 年，关于细致处理发射机抖动机制（如有损通道引起的抖动放大）的 IEEE 论文发表，作者为 Rao 博士。

时至今日，创新的步伐仍在继续，ADS 的通道仿真器被广泛视为行业标准。ADS 进一步拓展通道仿真器的功能。要更好地了解这些功能，请参阅以下两个示例：

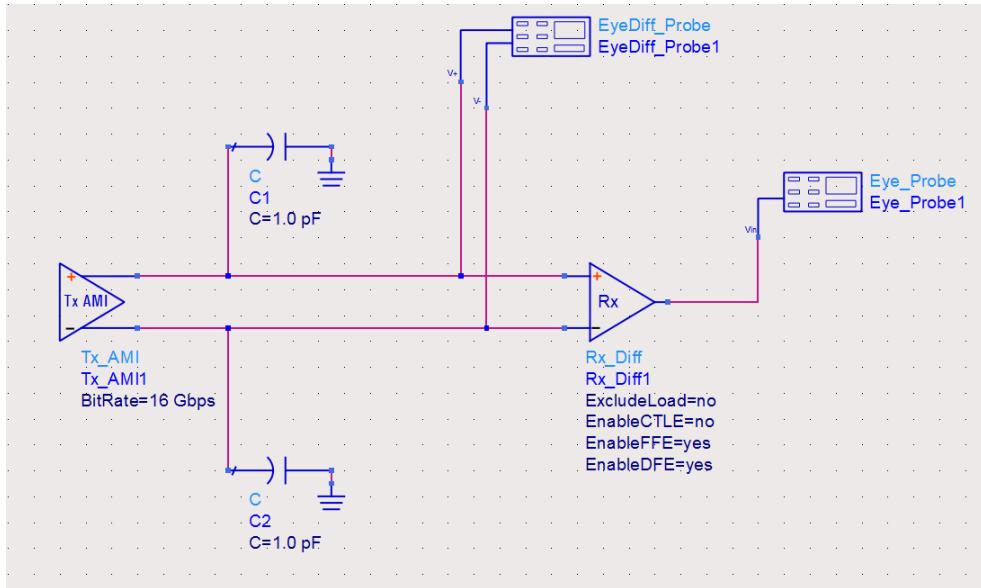

**示例 1：**设计人员 A 经常处于早期的版图前期设计阶段，没有选择特定的 IC 厂商。IBIS-AMI 发射机（Tx）模型在链路的一端，但是另一端没有合适的 IBIS-AMI 接收机（Rx）模型。重点是通道设计和需要提出某些版图约束条件，但是在接收机设置方面没有专业技术经验。他希望使用 ADS 中的通用接收机组件（Diff\_Tx），该组件可以计算接收机的最佳 FFE 和 DFE 抽头，甚至可以自适应调整接收均衡。

**解决方案：**在 ADS 中，设计人员可以使用 ADS 中的通用接收机组件（Diff\_Tx），它可以计算接收机的最佳 FFE 和 DFE 抽头，甚至可以自适应调整接收均衡。ADS 允许设计人员混合搭配 IBIS-AMI 模型和非 AMI 通用内置模型以及 SPICE（图 5）。此外，通道仿真器现在直接支持 IBIS 包（.pkg）条目，并且支持的范围比以前更广泛。它甚至可以在正式的 IBIS 解析程序发布之前便为 IBIS v6.1 提供标准前的支持。IBIS 模型的超频就是新 v6.1 内容的一个例子。

图 5. 借助 ADS，设计人员可以混合搭配使用 IBIS、IBIS-AMI、SPICE 和通用内置模型中的模型。

**示例 2：**设计人员 B 希望根据特定的链路规范进行设计，并且需要 Tx 和 Rx 模型。

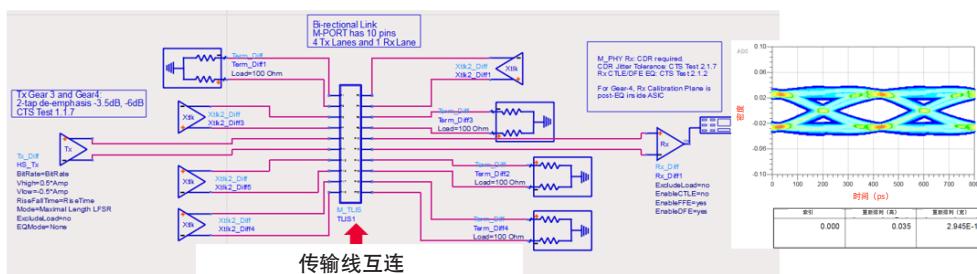

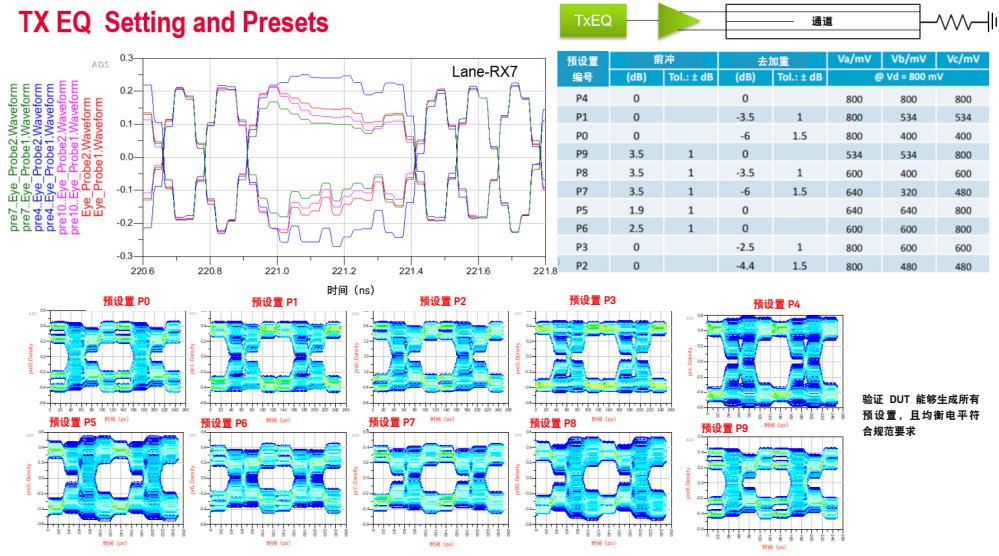

**解决方案：**ADS 包含用于 PCIe3、USB 3.1 和 100GbE 标准的 IBIS-AMI Tx 和 Rx 模型。这些模型附带一致性测试台和/或工作区模板。两个主要示例是用于 MIPI® C-PHY™、D-PHY™ 和 M-PHY® 的模板，以及用于 PCIe 3 标准 EQ 预设置的工作区，这些工作区已添加到 PCIe 3 一致性测试台中，可以用于批处理模式的仿真（图 6 和图 7）。

## M-PHY Simulation: High Speed NRZ Signaling

### - 参数化仿真设置

- 速度等级 1~4，A 和 B

- 大和小 Tx 幅度

- 负载端接或非负载端接

|     |                    |     |                    |

|-----|--------------------|-----|--------------------|

| VAR | High_Speed_Gears_A | VAR | High_Speed_Gears_B |

|     | HS_G1_A=1240 Gbps  |     | HS_G1_B=14576 Gbps |

|     | HS_G2_A=2*HS_G1_A  |     | HS_G2_B=2*HS_G1_B  |

|     | HS_G3_A=2*HS_G2_A  |     | HS_G3_B=2*HS_G2_B  |

|     | HS_G4_A=2*HS_G3_A  |     | HS_G4_B=2*HS_G3_B  |

|     |                        |     |                   |

|-----|------------------------|-----|-------------------|

| VAR | Large_Amplitudes       | VAR | R50_Term_Non_Term |

|     | HS_Amp_Large_RT=200 mV |     | RT=50 Ohm         |

|     | HS_Amp_Large_NT=400 mV |     | NT=10 KOhm        |

### - 互连模型

- 每个 M-PORT 上 10 个引脚，总共 5 个通道，有通道间或通道内耦合

- 在模型中包括 TxRx 封装、PCB 走线和过孔

图 6. ADS 为 MIPI M-PHY 仿真提供了一个模板。

图 7. ADS 拥有用于 PCIe 3 标准的 EQ 预设置，其已添加到 PCIe 3 CTB 中。

## 4. ADS 立身于技术（如 PAM-4）潮头

对于某些人而言，设计消费类产品时遇到的日常 SI 挑战无外乎降低复杂性，保护链路性能，同时降低生产成本。他们想方设法在使用便宜的有损材料且走线密集的印刷电路板中集成各种标准的高速链路。对于其他人而言，SI 挑战在于研究如何使用低损耗材料和制造工艺提高传输距离和速度，如生产数据中心使用的高速背板。背板上的走线通常采用更昂贵的制造方案，如背钻过孔 — 走线有足够的间距，在传输线上方和下方均具有界限明确的接地参考（通过过孔缝合良好，并且主要是实心面）。那么关键问题就变成了：对于材料和过孔设计以及制造厂的工艺变化，我需要知道什么，才能使链路达到 50 Gbps 的稳定速率？

当然，这两类 SI 专用软件也有很多的相似点。IP 路由器/服务器产品所面临的市场压力，要求它们的设计能够实现处理能力更强，而比特成本更低。随着我们对于数据的渴求增加，技术也需要齐头并进。但是，想要达到更快速率，以及在典型背板的距离内提供单一的 100 Gbps 电通道，这已经超越了现有技术的能力。为了达到所期望的数据速率，我们需要添加更多的数据通道。问题就再次回到了如何在电路板上走线了，因为 PCB 上已经没有多余的空间可以添加通道。消费类产品的设计人员也面临同样的问题。

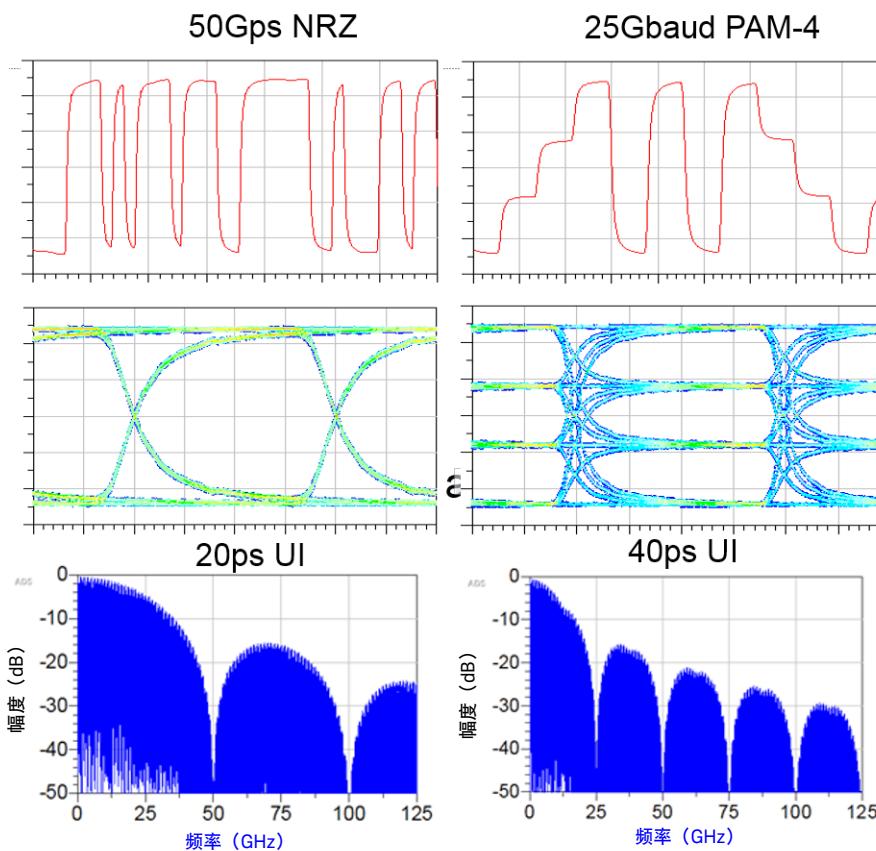

主要的解决方案可能是采用与非归零（NRZ）完全不同的信令标准，如图 8 所示，即用于高速串行链路的脉冲幅度调制（PAM）。它代表业界迈出了革命性的一步；然而，它也带来了一系列独特的挑战。例如，我们能以 28 Gbaud 发送一个 PAM-4 符号（每个电平代表两个原始比特），然后在另一端收到 56 Gbps。这样做的代价是集成电路功耗更大，信号本身的信噪比（SNR）降低，并且接收机的设计更为复杂。

图 8. PAM-4 是替代 NRZ 的可行方案。

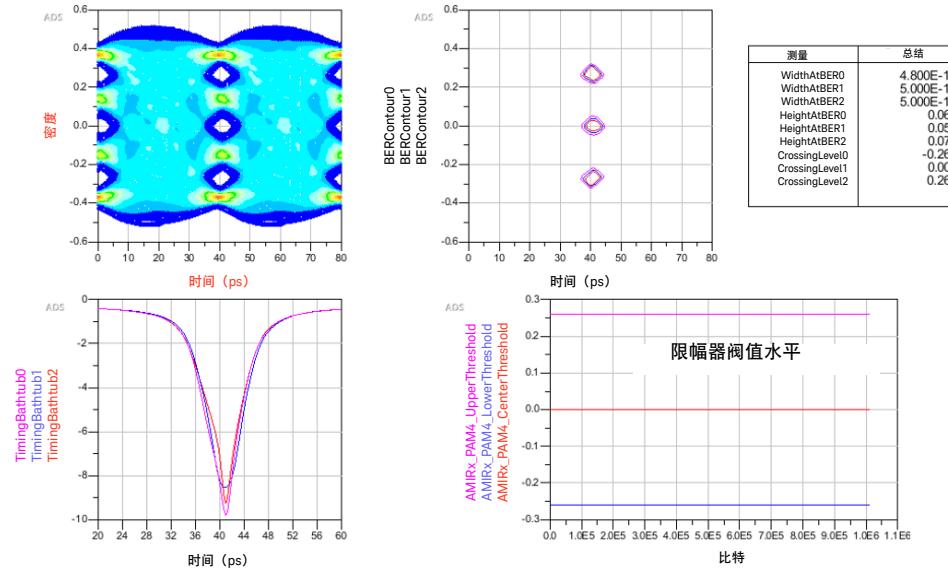

在接收机体系结构中，有三个限幅器判定信号是否超出 3 个阈值。为了改善符号误码率 (SER)，接收机可以独立控制每个判定限幅器，对判定的电压阈值进行自适应调整。此外，每个限幅器的采样时间可以分别调整，以应对偏离中心的眼图。时序也可以进行自适应调整。但是，在这样复杂的环境下，您如何进行 PAM-4 链路仿真？

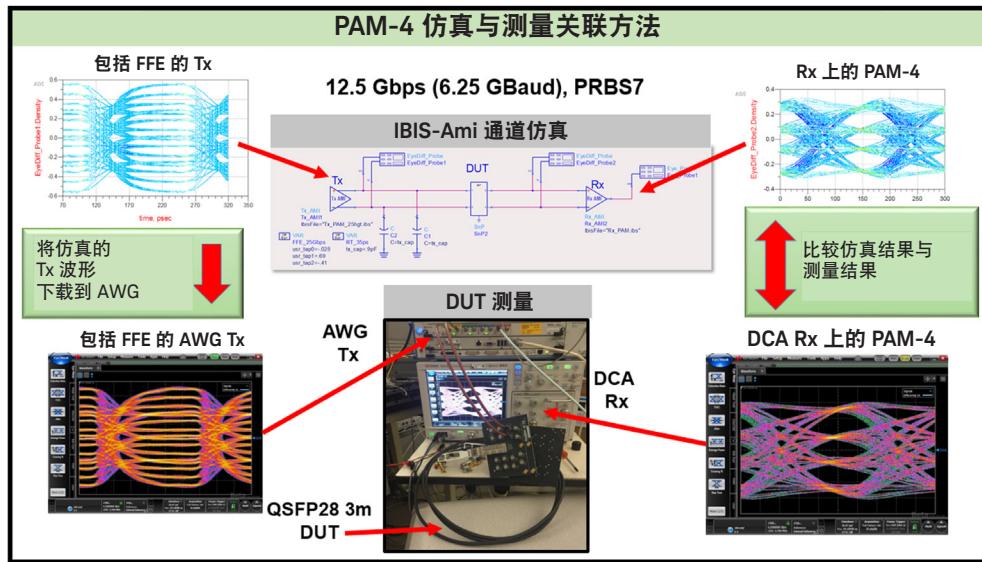

答案是双重的。克服这一挑战需要 EDA 厂商始终紧跟技术发展趋势，提供能够仿真和测量 PAM-4 信号的解决方案。Keysight EDA 就是这样一个值得信赖的供应商。它在 IBIS v6.1 标准制定之前便为 PAM-4 IBIS-AMI 模型提供通道仿真器技术。并且，它提供的 PAM-4 仿真技术是通过与领先 PAM4 集成电路厂商密切合作、共同设计完成的，这种技术能充分表征接收机的预期特性（图 9）。

为了测量 PAM-4 信号，Keysight EDA 的 ADS 提供通道仿真算法来测量每个眼图的 SER 曲线图，为每个眼图提供时序和电压曲线。

图 9. ADS 支持 PAM-4 仿真。

ADS 中的通道仿真算法与是德科技测试仪器中使用的测量算法相同。此外，ADS 通道仿真得到的波形可以传输给 Keysight FlexDCA，以便进行仿真与测量的关联。（关于此过程的更多信息，请参阅是德科技的 Heidi Barnes 发表的 DesignCon 2016 论文：<http://literature.cdn.keysight.com/litweb/pdf/5992-1320EN.pdf>）。在此，Keysight EEsof EDA 提供了一种方法来校准仿真和测量结果，进而实现更快的数据速率。

图 10. ADS 通道仿真波形可以传输到 FlexDCA 中，进行仿真与测量的关联。

## 5. ADS 加速 DDR4 仿真方法

通常，DDR 仿真工具包中最重要的工具就是 SPICE（瞬态）仿真。信号间的时延（偏移）、数据线、命令/地址线和控制线上的建立和保持时间（需要多长时间才能达到高电压阈值，以及能在该阈值上保持多久）等测量，对于存储器设计人员而言都十分熟悉。但是，这些同样的设计方法在 4266 MHz 上是否与在 1333 MHz (DDR3) 一样适用？这个问题的答案具有双重性，因为 DDR4 JEDEC 规范中沿用了一部分传统测量，同时也采用了一部分全新的、改进过的测量。

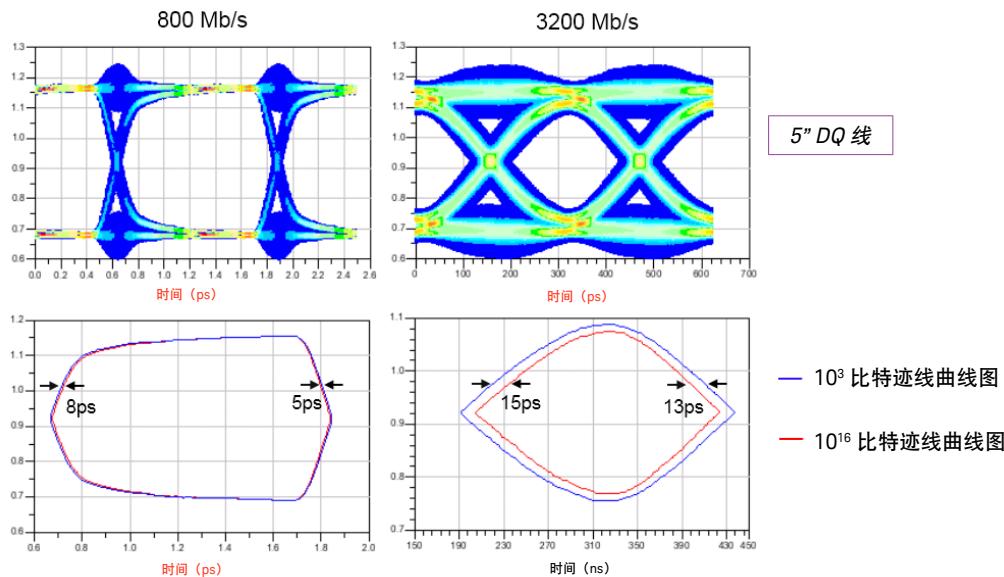

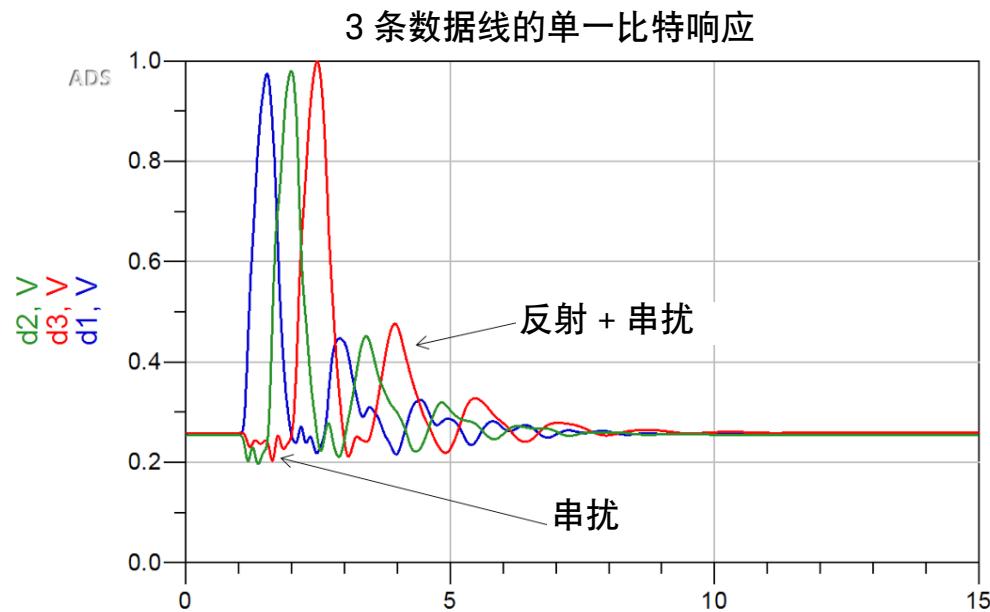

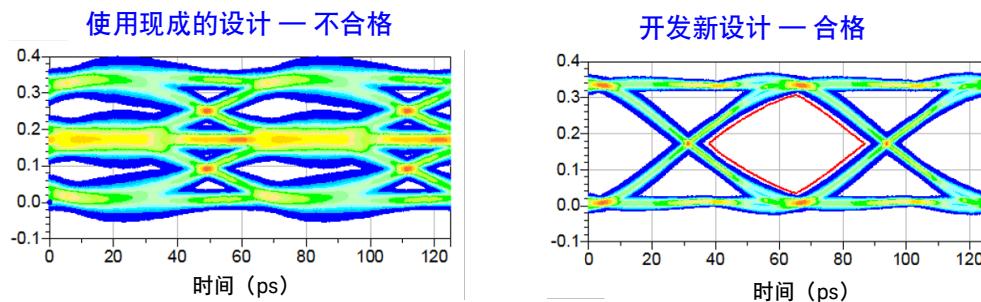

问题在于，在更快的速度下，随机性抖动和确定性抖动影响更大，占据了眼图（即单位间隔 (UI)）中相当大的比例，如图 11 所示。物理长度相同的走线此时在任意时间点上传输的比特数更多（例如电长度更长 = 波长更多），这意味着任何阻抗不匹配（一个比特的反射）都会导致符号间干扰 (ISI)，从而影响其后更多的比特。邻近走线的串扰只是增加了干扰（图 12）。

图 11. 在更快的速度下，随机性抖动和确定性抖动会占据眼图中相当大的比例。

图 12. 阻抗不匹配导致 ISI。来自附近走线的串扰增加了干扰。

作为设计人员，您可以使用瞬态仿真器仿真通过通道的 1 百万比特，并成功通过所有传统测试。然后，您可能使用新的随机比特流进行第二次仿真，却不能通过其中某项测试，这是为什么呢？首先，这就是随机性抖动的本质，它的统计曲线图有一个长拖尾。一致性极限值要有多大的裕量才足以确保稳健运行？其次，当我们从 ISI 中发现眼图质量的最大下降时，仿真的比特流组合数量呈指数级增长；也就是说，这是比特流码型的“最坏情况”。最坏情况的比特流是受干扰线和每个串扰干扰线上的一组独特数据码型，这会导致眼图严重坍塌。

从另一方面讲，我们需要可靠的高性能存储器系统。大多数人都了解存储器所起到的关键作用，并且亲身经历过因存储器故障导致的系统崩溃。这就是 JEDEC 针对数据线推出全新 BER 接收机模板测试的原因。一致性测试模板的概念借鉴了高速串行通信标准。它允许将数据线设计为满足 BER 目标（ $1e-16$  和更低），而无须受到设计约束条件的过多限制，否则会增加成本并延缓产品上市。

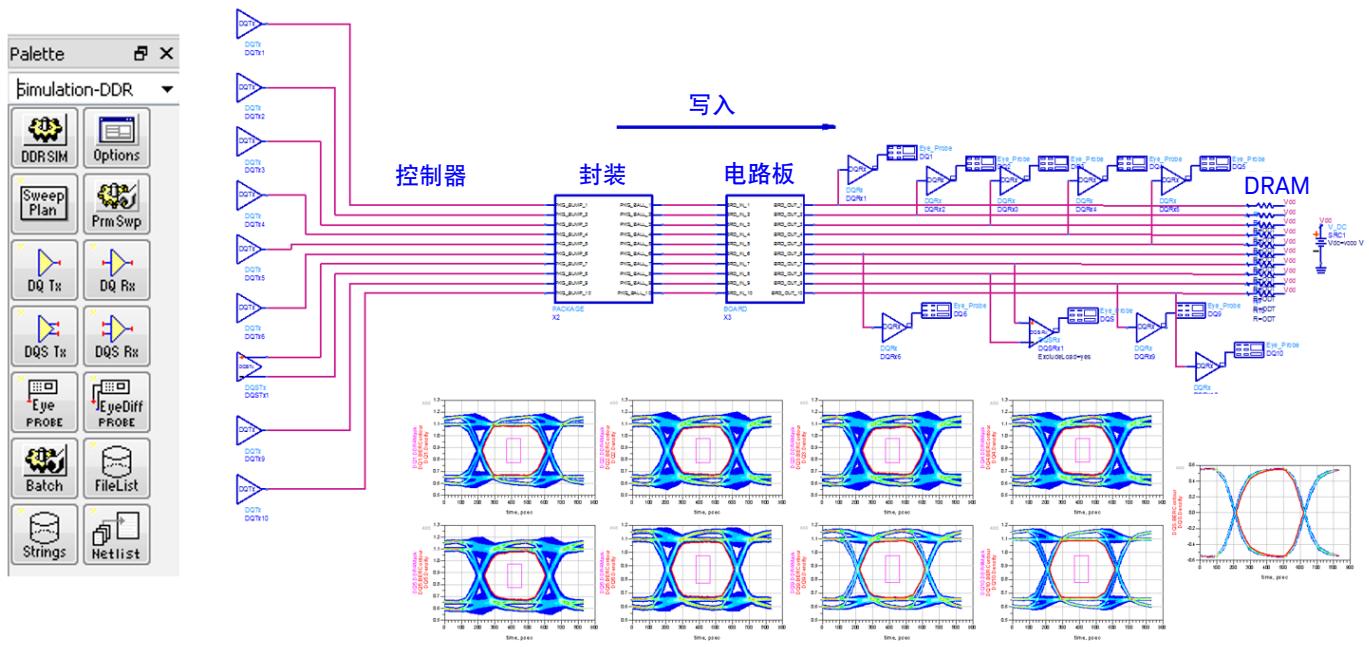

这样就带来了一个重要问题：在仿真中，您如何对模板的一致性进行检查？Keysight EDA 提供了一款专为此任务设计的新型 DDR 总线仿真器。它是用于并行总线的逐位通道仿真器（图 13）。它可以一次表征所有发射机路径，并计算接收端每个眼图的 BER 曲线图，同时测量模板裕量。该仿真器的独特之处在于它可以正确处理单端信号上不对称的上升沿和下降沿。此外，发射机和接收机模型可用于驱动 IBIS 模型，或与 SPICE 模型混合使用。仿真器的速度使得它能够在许多版图前期任务中代替瞬态仿真，在这些任务中，设计人员要扫描多个参数（通道配置）或进行调查以改善性能。它与批仿真一起可用作版图前期设计探索的有用工具，也可以用于版图后期的一致性验证。

图 13. Keysight EEsof EDA 的 DDR 总线仿真器是用于并行总线的逐位通道仿真器。

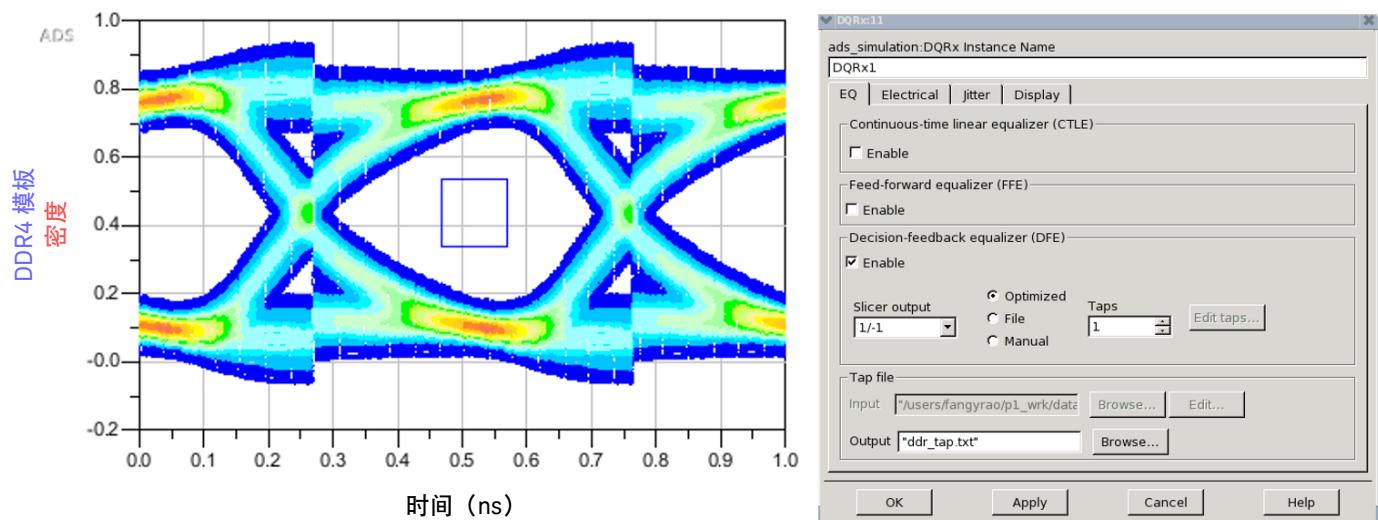

为了对这些功能做进一步补充, ADS 现在增加了对接收机均衡 (CTLE、FFE、n 抽头 DFE) 的内置支持, 如图 14 所示。这一需求主要来自开发存储器控制器集成电路的企业, 他们尝试最大限度提高链路裕量, 尤其是针对线路较长的服务器存储器体系结构上的 DQ、DQS 和 CLK 信号。是德科技的优势在于它能够提供包含均衡的单端接收机模型, 该模型不会干扰精确通道仿真的线性时不变要求。

图 14. ADS 引入了对接收机均衡的支持, 以加速 DDR4 仿真。

## 6. ADS 将电源交到设计人员（PI 分析）手中

近年来，电源完整性（PI）已发展出自己的专门技术领域。简而言之，它的目标是确保系统中的集成电路接收到所需的电压和足够的电流，以便正确地工作。首先是确定能否为有需求的每个集成电路（如接收机）提供正确的直流电压和电流。一开始，这项任务看起来只需非常简单的计算。然而，电源完整性已经成为现代高速系统中与日俱增的挑战，它主要受到以下两个方面的影响：

1. 器件集成度更高，集成电路电源电压更低

- 电压越低，每个器件引脚上需要的电流就越大，从而导致直流压降越大。

- 电压越低，控制 DC-IR 压降的要求就越严，以满足接收机的  $\pm 5\%$  典型电压要求，这意味着允许的直流压降更小。

- 器件集成度越高，集成电路周围的走线就越致密，从而导致电源网络中的电流密度更高，直流压降也更大

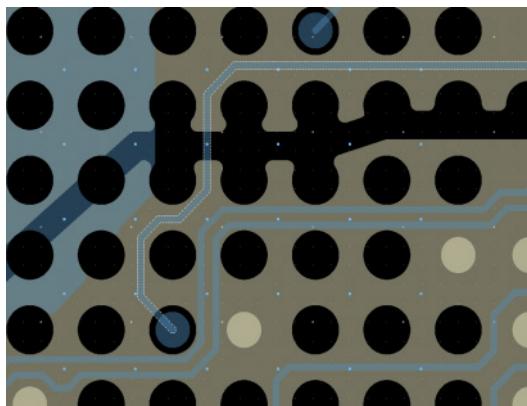

2. 收缩 PCB 实现更小的外形尺寸。PCB 上的空间更小，使得信号走线更加密集，没有多少地方留给宽敞的电源面。这样的结果是，电源面和接地都被其他网络过孔周围的间隙孔（反焊盘）穿透（图 15）。由于层面有很多孔洞，显然可供电流流动的路径现在更细，因此，它的电阻更大，导致直流压降也更大。

图 15. 如果 PCB 的尺寸收缩，电源面和接地都被间隙孔大量穿透。

过去，在笔记本上进行计算就已经足以处理 PI。然而，在现代设计中，一个真正的 PI-DC 仿真器需要考虑到配电网络（PDN）的实际物理版图以及材料的输入，如过孔的电镀厚度（因为过孔的金属厚度对直流压降计算有很大影响）。

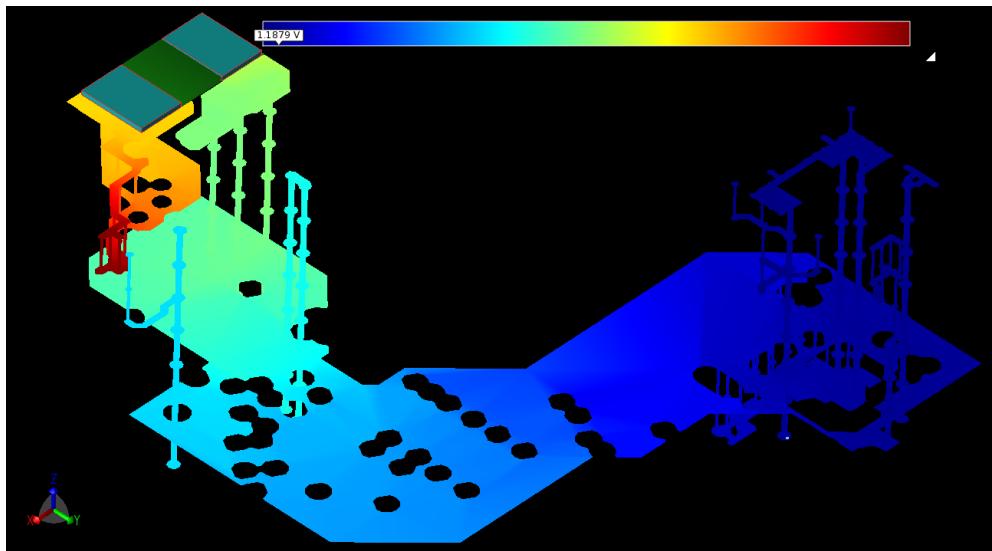

EM 仿真器的 PIPro 套件为此提供了出色的解决方案。有了专用的 PI-DC 仿真器之后，只需几秒钟，设计人员就可以看到反馈信息，确切掌握所选电源和接地网的电压分布情况（图 16）。

图 16. 设计人员能在几秒钟内看到所选电源和接地网的分布情况。

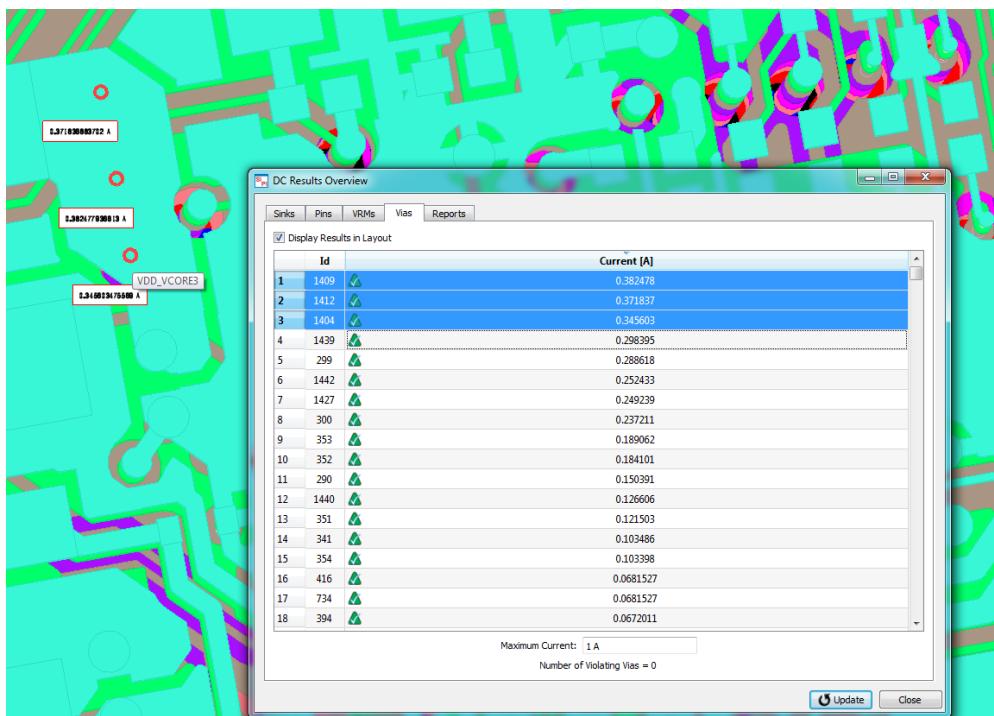

ADS 还允许设计人员检查通过各个过孔的电流以及特定位置的电压和电流，例如接收机和电压调整模块（VRM）上的各个引脚。这些信息通过可排序表格报告。承载过多电流的过孔可以在版图中突出显示以便识别（图 17）。

图 17. 承载过多电流的过孔可以在版图中突出显示以便识别。

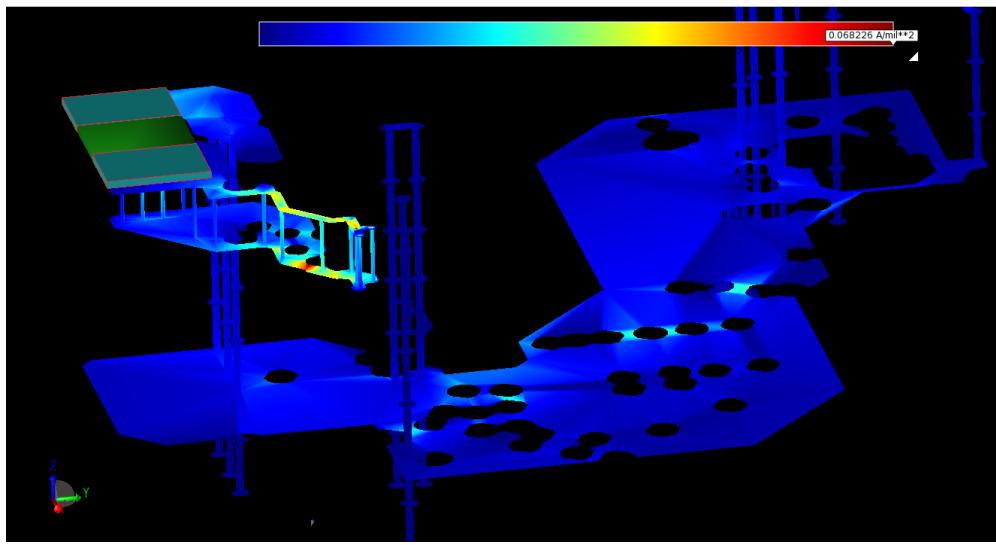

在直流环境下，设计人员通常尝试设计电阻为低  $m\Omega$ （例如小于  $100 m\Omega$ ）的 PDN。通过查看电流密度，找出电阻较高的区域，能立即为他们如何更好地改进设计提供参考。ADS 让这一切美梦成真（图 18）。

图 18. 借助 ADS，设计人员可以轻松找出电阻较高的区域。

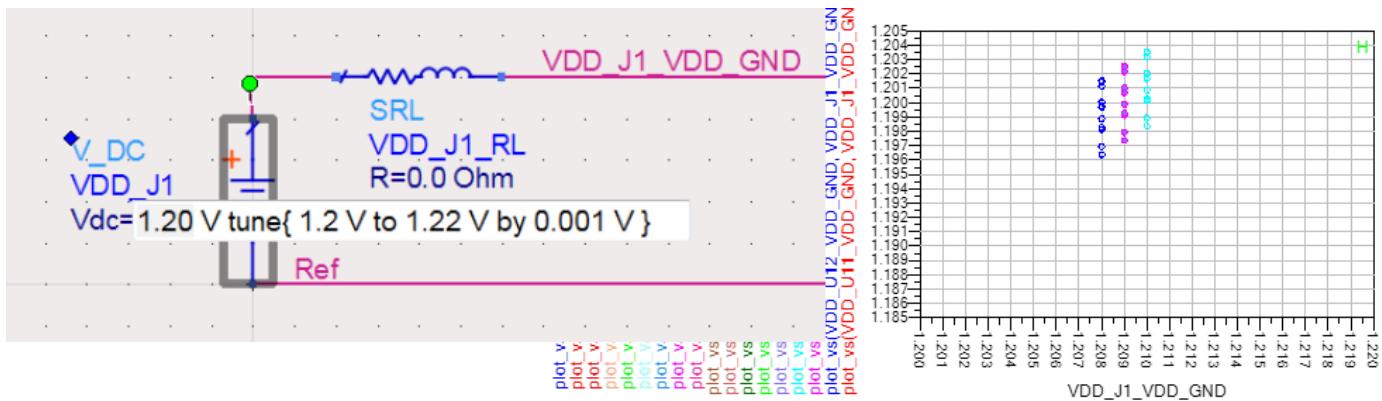

电源电压调整模块 (VRM) 的位置是设计的关键。一个 VRM 可以为多个接收机供电，某些 VRM 可能配有“感应线”，也就是从靠近接收机的主 PDN 而来的反馈线。感应线为 VRM 提供输出电压电平信息，以便对输出电压进行相应的调整。这样就带来了一个问题：如何检查 VRM（配有感应线）是否给最远的接收机提供了足够的电压，同时又不会给最近的接收机提供过高电压？

有了 ADS，设计人员可以使用 PIPro 自动生成的原理图来获得 PDN 的 EM 精确模型以及 VRM 和接收机的电路模型。然后，设计人员必须调谐 VRM，来验证输出电压设置是否能够满足各接收机的要求（图 19）。

图 19. 借助 PIPro，设计人员可以检查 VRM（配有感应线）是否给最远的接收机提供足够的电压，同时又不会给最近的接收机提供过高电压。

## 7. ADS 可实现平坦的 PDN 阻抗响应

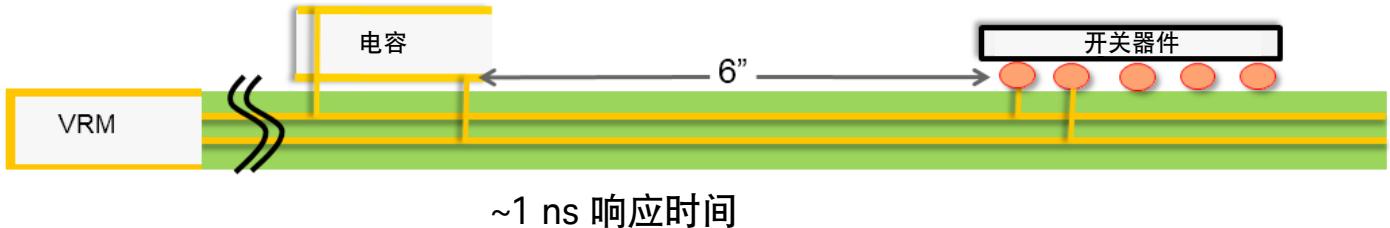

虽然从直流角度考虑电源完整性非常重要，但是，从交流角度考虑也同样重要。在 PDN 中，有多个集成电路用作接收机，每个集成电路以不同的频率开关。它们的电流消耗不是恒定的，根据所进行的操作，负载随时间从低阻抗变为高阻抗。当接收机切换到低阻抗时，VRM 做出响应并提供额外电流所需的时间受到 PCB 上电信号速度的限制。其传播速度大约为 166 ps/英寸，意味着如果信号源和接收机之间相距 6 英寸，那么在响应开关器件突然的阻抗变化时会产生约 1 ns 的时延（图 20）。

图 20. 如此所示，信号源和接收机之间有 6 英寸的间隔，响应开器件突然的阻抗变化会有约 1 ns 的时延。

通过缩短间隔并在 VRM 和接收机之间放置更多的去耦电容，我们可以提供电荷的本地存储，将突发电流请求时的响应时间控制到最短。在理想情况下，我们可以将大容量电容置于 VRM 附近，中等容量电容置于板上集成电路周围，而将小容量电容置于封装内，同时集成电路上已经存在片上电容。电容的大小也会影响我们尝试提供电源的工作频率（分别为低频、中频和高频）。

描述这种情形的另一种方法是，假设电流到达接收机并通过接地网返回，这个电流回路就会产生一个磁场，能够储存能量。该磁场能阻止电流的进一步变化，换句话说就是存在电感。此电流回路的电感与回路的长度成正比。电流回路越长，电感就越高。PDN 阻抗  $Z = R + j\omega L - j/\omega C$ ，其中， $\omega$  是角频率。我们可以看到，在高频下，电感会导致 PDN 的阻抗升高，但这可以通过小电容 (nF 和 pF) 抵消。也就是说，如果以高频开关接收机，且电流回路较长，那么接收机不会收到它所需的额外电流，除非我们有一个工作在该频率下的本地电容。

遵循集成电路厂商的指导和/或在电路板上放置尽可能多的去耦电容并不足以打造强大的 PDN 设计。实际上，有两个关键因素需要考虑。第一个因素是物料清单 (BOM)。由于板上有多个 PDN 且空间有限，同时考虑到降低制造成本的压力，在 PDN 的设计上没有多少裕量可留。利用仿真推断同一 PDN 上不同电容之间的耦合，可以立即让设计人员知道电容之间的回路电感是高还是无关紧要。如果没有去耦电容的回路阻抗很小，那么可以去掉去耦电容。

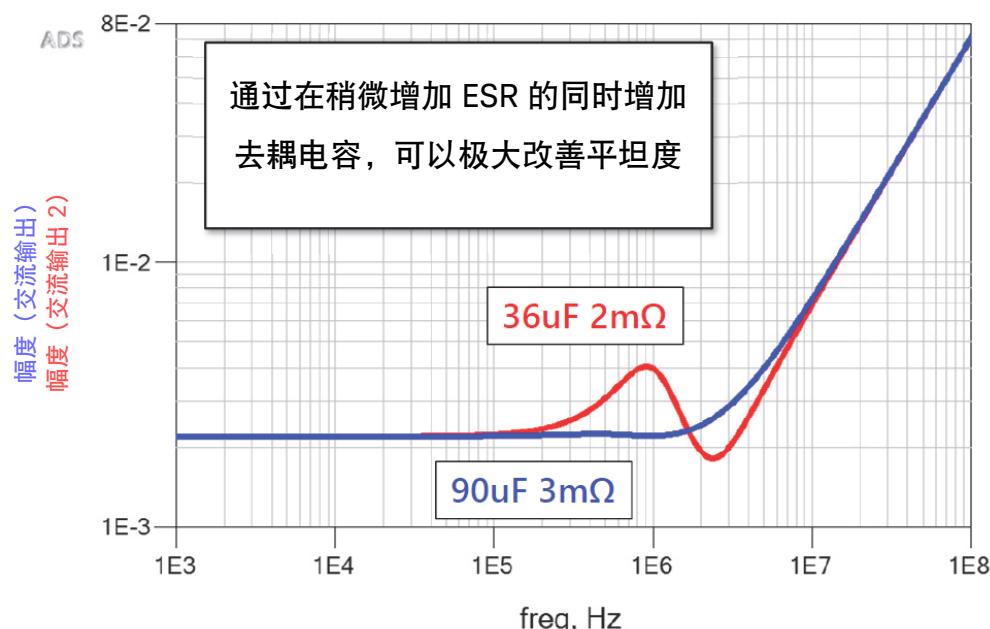

第二个要考虑的因素是，电容绝不仅仅是电容。表面贴装电容总会有等效串联电阻（ESR）和等效串联电感（ESL）。这意味着，SMT 元器件与频率有很大关系。实际上，随机放置额外的去耦电容不是一个好主意，因为它会导致 PDN 内出现多余的谐振。

想要进行非常精确的 PDN 仿真，我们强烈建议使用 SMT 部件的 S 参数模型（图 21）。但是，请注意，当我们有两个物理距离上接近，且具有不同 ESR 值的去耦电容时，结果可能非常令人吃惊。阻抗曲线中产生了谐振（高 Z）和反谐振（低 Z）。这与我们通过精心的 PDN 设计想要达到的效果背道而驰。

图 21. 在增加 ESR 的同时增加去耦电容，可以改善阻抗响应平坦度。

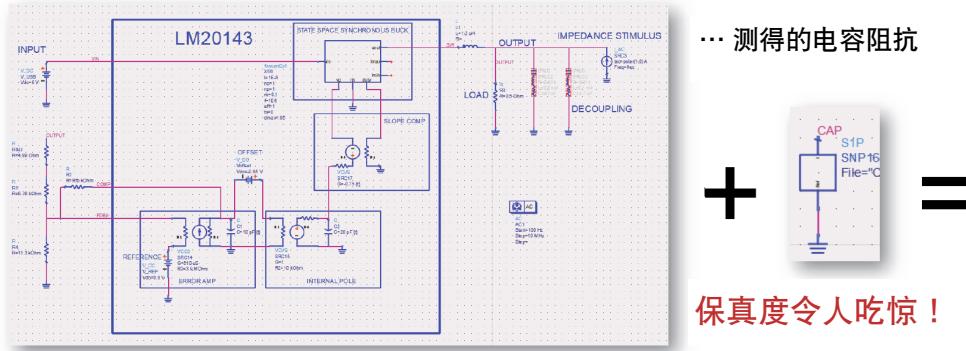

理想的 PDN 中，接收器件将能够承受集成电路厂商规定的足够电压和电流。PDN 还将拥有成本最低的 BOM，并且本身非常稳定。来自 PicoTest（是德科技渠道合作伙伴）的 Steven Sandler 是知名的电源完整性专家，具有超过 35 年的行业经验，并且就这个主题发表过多部专著。Steven 认为，进行非侵入性稳定性测量要分为几个步骤，然后测量和表征 VRM 得到基于状态的特性模型。VRM 本身是非线性的，并具有反馈补偿机制，这些机制可以通过基于状态的模型加以表征。Steven 认为，稳定的 PDN 是不会产生谐振的（图 22），所以配合使用这个模型与 VRM 的高保真度特性模型，设计人员可以设计实现平坦的阻抗响应。

图 22. 稳定的 PDN 没有共振。

一旦初始版图前期设计创建完毕，设计人员可以将一次通过的 PCB 版图导入到 ADS，并运用 PIPro EM 技术进行分析。PIPro 的网络驱动用户界面允许设计人员为其希望仿真的 PDN 网络快速选择电源和接地网，为每个元器件（例如去耦电容、EMI 滤波器、电感、电阻等）选择仿真模型，并设置 PI-AC 仿真器来计算元器件就位后版图的 PDN 阻抗。

由于 PI-AC 仿真器应用了专门为此设计的 EM 技术，因此几分钟之内即可返回非常准确的结果。设计人员可以使用 ADS 的场可视化、PDN 阻抗和 S 参数绘图来确定当前的 PDN 设计是否存在问题是，并逐一检查电容的耦合。只需点击一次，即可生成原理图，将 EM 表征模型连同元器件的电路模型一并发送。对 ADS 原理图的这种反向注释，可实现流畅的内聚型工作流程。然后，设计人员可以应用其特性 VRM 模型，进一步调谐去耦电容进行最终的验证/优化。

## 8. ADS 提供电热仿真

由于电力传输网络被迫采用外形更加紧凑的 PCB，因此电源面的位置与理想位置差距甚远。曾经完美的平面通常会被缝合过孔的间隙孔大量穿透，版图工程师很难在不经过狭窄金属走线的情况下将所需的电流封装到需要它的器件中。计算准确的 IR 压降对于电源完整性设计人员来说非常重要，但了解 PDN 走线、过孔和芯片将达到的绝对温度也同样重要。高温会导致可靠性问题，因为开/关状态下的温度循环会导致过孔壁逐渐变得脆弱和破裂。

设计人员不能直观地判断过孔的尺寸是否匹配流经它的电流。温度上升很大程度上取决于与其相连的走线的宽度。其次，走线的电阻随温度增加，需要进行仿真分析来确定最终的稳态条件。我们发现，温度每改变 10 °C 走线的电阻会改变 4%。这些观察结果表明，我们需要使用 DC IR 压降电热解决方案来仿真 PDN 设计。

ADS 提供全自动的综合电-热-电迭代仿真。考虑到加热引起的局部电阻率变化，用户可以获得 DC IR 压降结果的更准确表述。附带的纯热仿真让用户能够执行热本底规划。

使用 ADS，您可以轻松地将现有的 DC IR 压降仿真设置复制到新的电热仿真中，并可以查看平面、引脚和过孔的温度列表。

图 23. 直流 IR 压降电热分析 — 温度可视化显示。

## 9. ADS 有一个互连工具箱 (Via Designer 和 CILD)

信号完整性设计挑战不仅仅需要在接收机上成功复原发射机信号，还要了解影响性能的因素。哪些因素消耗的裕量最大？我们可以进行哪些方面的优化？

发射机和接收机之间的典型连接包含某些部分的专用定制 PCB 布线。ADS 具有信号完整性工具箱，可帮助探索设计权衡，处理堆叠、传输线损耗和过孔拓扑之间的复杂关系。

设计 PCB 互连时，首先要定义某种 PCB 堆叠，这样是为了开始对各种不同类型的候选传输线拓扑进行评测。一旦传输线针对阻抗和损耗进行了优化，我们就需要考虑过孔在各层之间进行转换的性能。

这些步骤中的任何一步都会给其他步骤的成本和性能带来影响，导致在确定哪个特性真正地消耗裕量时需要考虑它们复杂的相互关系：层数、线路阻抗、背钻过孔、材料、版图密度等。

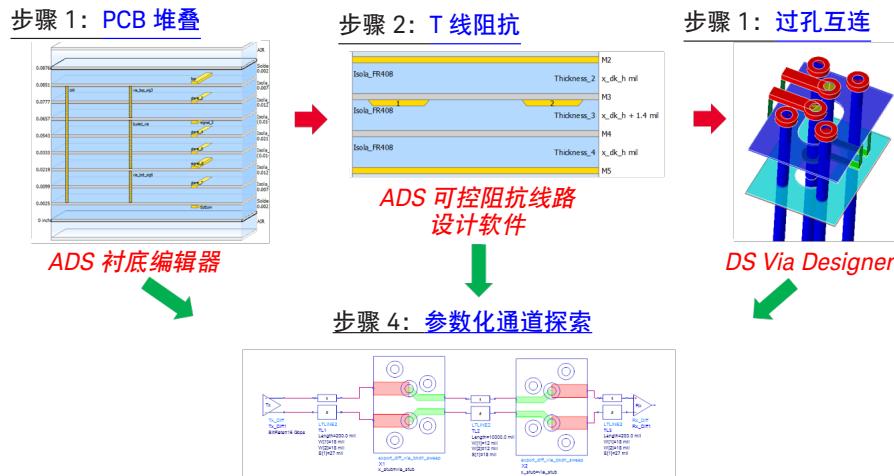

ADS 提供了一个互连工具箱，其中包括衬底编辑器、可控阻抗线路设计软件和 Via Designer，可以简化版图前期的 pcb 互连调查。

如果您的堆叠结构与参考设计不匹配，那么您需要在开始版图设计前做一些版图前期调查。ADS 中的流程如下：

- 第 1 步：在衬底编辑器中输入 PCB 堆叠并定义所需的变量。

- 第 2 步：使用可控阻抗线路设计软件创建自定义 T 线-线类型模型。

- 第 3 步：使用 Via Designer 创建互连过孔的参数化 3D-EM 模型。

- 第 4 步：在 ADS 时域和频域仿真器中运行堆叠、T 线-线类型和 Via Designer EM 模型中配置的参数值，以优化关键性能，如眼图打开或 BER。

逐步完成整个流程。ADS 衬底编辑器最近发布了许多增强功能来处理多层 PCB。除了图形查看器和编辑器之外，我们还可以在表编辑器中将值一次性复制并粘贴到多个层。如果您利用现成的设计，强大的 ODB++ 导入功能可捕获层定义并调取表信息。新工作区还可以选择自动生成通用堆叠，以避免手动输入。

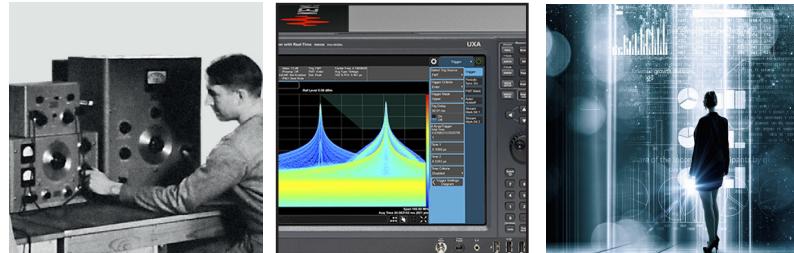

## 10. ADS 传递是德科技理念：人力资源、硬件和软件资源的结合，开启测量新视野

从惠普，到安捷伦科技，再到是德科技，我们的理念一脉相承，努力成为世界上首屈一指的设计、测试与测量公司。除了悠久的公司历史、良好的企业文化之外，我们引领市场的决心从未动摇，贯穿始终。

在高速数字领域，有三位是德科技的技术骨干担任 JEDEC、VESA 和 PCI-SIG® 的理事。另有四位骨干在 MIPI、IEEE 以太网、OIF、SATA、SAS、UFS、HDMI 和 USB-IF 等组织中担任要职。是德科技在超过 15 个标准机构内派驻了代表，同时还密切关注很多其他组织的动向（图 23）。这意味着，我们有许多专家对新兴标准所带来的挑战有着深刻的认识。

|                                     |                                         |                      |                           |                                     |                           |                                     |                             |                                                   |

|-------------------------------------|-----------------------------------------|----------------------|---------------------------|-------------------------------------|---------------------------|-------------------------------------|-----------------------------|---------------------------------------------------|

| 存储器<br>Perry Keller                 | DisplayPort<br>Brian Fetz               | USB<br>Jit Lim       | 计算机<br>Ricks Eads         | 光<br>(元器件)<br>Greg LeCheminant      | 光学 WAN<br>Stefan Loeffler | HDMI<br>Stefan Friebe               | 存储<br>Matthew Woemer        | MIPI<br>Roland Scherzinger                        |

| 监事会<br>JEDEC<br>一致性测试<br>主管<br>UFSA | 校友会校友<br>VESA 物理<br>小组<br>USB-IF<br>一致性 | 影响因素<br>USB-IF       | 校友会校友,<br>PCI-SIG         | 影响因素<br>IEEE,<br>OIF-CEI,<br>T11 FC | 影响因素<br>OIF, ITU, IEC     | 影响因素<br>HDMI<br>BoD (Thomas Dippon) | 影响因素<br>SATA-IO,<br>T10 SAS | TSG 成员<br>UniPro<br>副主席<br>MIPI 联盟<br>Thunderbolt |

| LPDDR4, UFS                         | DP 1.3<br>USB Type-C™                   | USB<br>2.0, 3.0, 3.1 | PCIe G3, G4,<br>PAM4 (RT) | PAM-4 (Opt),<br>CEI 3.1             | PAM-4 (Opt),<br>CEI 3.1   | HDMI 2.0                            | SAS-3                       | D/M/C-PHY,<br>UniPro, TBT                         |

图 23. 是德科技在各种新兴标准委员会中有技术负责人。

随着是德科技更多地关注以软件为中心的解决方案, Keysight EEsof EDA 将在虚拟一致性测试领域发挥主导作用。通过 ADS 中的一致性测试台, 设计人员现在可以获得 ADS 仿真的波形, 并采用理想的一致性测试套件对其进行测试, 以树立设计符合标准的坚定信心 (该套件与测试台上与最终验证硬件一起使用的套件相同)。ADS 提供 USB 3.1、PCIe® G3、HDMI 2.0 和 100GbE 一致性测试台的更新。

Keysight EEsof EDA 为客户提供支持, 进一步强化 ADS 的这些功能。这种支持包括全球性的技术支持、专家级应用工程师和顾问型的销售工程师。这种有力的支持与是德科技的硬件和软件解决方案以及专业技术相结合, 可以为客户提供更好的洞察力, 帮助其获得更大的成功机会。

## 结论

多年以来, ADS: 已成为业界闻名的电子设计自动化软件, 适用于射频、微波和信号完整性应用。随着在电路仿真、版图和版图验证、硅 RFIC 以及至关重要的信号和电源完整性方面的不断发展, ADS 进一步巩固了这一地位。ADS 用来解决现代 SI 和 PI 问题的各种工具、EM 技术和方法已经显著提升了仿真和分析 SI 和 PI 设计任务的性能、准确性和效率。这意味着今天的设计人员可以拥有所需的能力, 迅速克服以往极为棘手的 SI 和 PI 设计挑战。如欲了解更多信息, 请访问 [www.keysight.com/find/eesof-hsd](http://www.keysight.com/find/eesof-hsd)。

## 下载软件, 为您开辟测量新视野

是德科技软件将我们渊博的专业技术集于一身, 供您轻松下载使用。从设计首次仿真到产品首次装运, 是德科技软件工具能够帮助工程师团队加快从数据采集到信息处理再到有效分析的过程。

- 电子设计自动化 (EDA) 软件

- 应用软件

- 编程环境

- 实用软件

如欲了解更多信息, 请访问:

[www.keysight.com/find/software](http://www.keysight.com/find/software)

开始 30 天免费试用。

[www.keysight.com/find/free\\_trials](http://www.keysight.com/find/free_trials)

如欲获得是德科技的产品、应用和服务信息, 请与是德科技联系。如欲获得完整的产品列表, 请访问: [www.keysight.com/find/contactus](http://www.keysight.com/find/contactus)

### 是德科技客户服务热线

热线电话: 800-810-0189、400-810-0189

热线传真: 800-820-2816、400-820-3863

电子邮件: [tm\\_asia@keysight.com](mailto:tm_asia@keysight.com)

### 是德科技 (中国) 有限公司

北京市朝阳区望京北路 3 号是德科技大厦

电话: 86 010 64396888

传真: 86 010 64390156

邮编: 100102

### 是德科技 (成都) 有限公司

成都市高新区南部园区天府四街 116 号

电话: 86 28 83108888

传真: 86 28 85330931

邮编: 610041

### 是德科技香港有限公司

香港铜锣湾希慎道 33 号

利园 1 期 45 楼 4567 室内

电话: 852 31977777

传真: 852 25069233

### 上海分公司

上海市虹口区四川北路 1350 号

利通广场 19 楼

电话: 86 21 26102888

传真: 86 21 26102688

邮编: 200080

### 深圳分公司

深圳市福田区福华一路 6 号

免税商务大厦裙楼东 3 层 3B-8 单元

电话: 86 755 83079588

传真: 86 755 82763181

邮编: 518048

### 广州分公司

广州市天河区金穗路 62 号侨鑫国际中心 17 楼

雷格斯侨鑫国际中心 1772 室

电话: 86 20 38390680

传真: 86 20 38390712

邮编: 510623

### 西安办事处

西安市碑林区南关正街 88 号

长安国际大厦 D 座 501

电话: 86 29 88861357

传真: 86 29 88861355

邮编: 710068

### 南京办事处

南京市鼓楼区汉中路 2 号

金陵饭店亚太商务楼 8 层

电话: 86 25 66102588

传真: 86 25 66102641

邮编: 210005

### 苏州办事处

苏州市工业园区苏华路一号

世纪金融大厦 1611 室

电话: 86 512 62532023

传真: 86 512 62887307

邮编: 215021

### 武汉办事处

武汉市武昌区中南路 99 号

武汉保利广场 18 楼 A 座

电话: 86 27 87119188

传真: 86 27 87119177

邮编: 430071

### 上海MSD办事处

上海市虹口区欧阳路 196 号

26 号楼一楼 J+H 单元

电话: 86 21 26102888

传真: 86 21 26102688

邮编: 200083

## 演进

我们独有的硬件、软件和技术人员资源组合能够帮助您实现下一次突破。

我们正在开启技术的未来。

从惠普到安捷伦再到是德科技

### myKeysight

#### myKeysight

[www.keysight.com/find/mykeysight](http://www.keysight.com/find/mykeysight)

个性化视图为您提供最适合自己的信息!

### 是德科技服务

#### **KEYSIGHT SERVICES**

Accelerate Technology Adoption.

Lower costs.

#### [www.keysight.com/find/services](http://www.keysight.com/find/services)

我们拥有业界领先的技术人员、流程和工具, 可以提供深度的设计、测试和测量服务。最终的结果就是: 我们帮助您应用新的技术, 而工程师为您改进流程并降低成本。

### 是德科技保证方案

#### [www.keysight.com/find/AssurancePlans](http://www.keysight.com/find/AssurancePlans)

10 年的周密保护以及持续的巨大预算投入, 可确保您的仪器符合规范要求, 精确的测量让您可以继续高枕无忧。

#### [www.keysight.com/go/quality](http://www.keysight.com/go/quality)

### 是德科技公司

#### DEKRA 认证 ISO 9001:2015

### 质量管理体系

DEKRA Certified

ISO 9001 Quality Management System

### 是德科技渠道合作伙伴

#### [www.keysight.com/find/channelpartners](http://www.keysight.com/find/channelpartners)

黄金搭档: 是德科技的专业测量技术和丰富产品与渠道合作伙伴的便捷供货渠道完美结合。

#### [www.keysight.com/find/solution](http://www.keysight.com/find/solution)

Unlocking Measurement Insights

本文中的产品指标和说明可不经通知而更改

© Keysight Technologies, 2018

Published in USA, November 26, 2018

出版号: 5992-1428CHCN

[www.keysight.com](http://www.keysight.com)