## N5991HP1A HDMI 2.1 Receiver Compliance Test Automation Software - User Guide

## **Notices**

#### © Keysight Technologies 2024

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

## Manual Part Number N5991-91501

#### Edition

Edition 5.1, July 2024

Keysight Technologies Deutschland GmbH Herrenberger Strasse 130, 71034 Böblingen, Germany

## **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

## U.S. Government Rights

The Software is "commercial computer software," as defined by Federal Acquisition Regulation ("FAR") 2.101. Pursuant to FAR 12.212 and 27.405-3 and Department of Defense FAR Supplement ("DFARS") 227.7202, the U.S. government acquires commercial computer software under the same terms by which the software is customarily provided to the public. Accordingly, Keysight provides the Software to U.S. government customers under its standard commercial license, which is embodied in its End User License Agreement (EULA), a copy of which can be found at http://www.keysight.com/find/sweula. The license set forth in the EULA represents the exclusive authority by which the U.S. government may use, modify, distribute, or

disclose the Software. The EULA and the license set forth therein, does not require or permit, among other things, that Keysight: (1) Furnish technical information related to commercial computer software or commercial computer software documentation that is not customarily provided to the public; or (2) Relinguish to, or otherwise provide, the government rights in excess of these rights customarily provided to the public to use, modify, reproduce. release, perform, display, or disclose commercial computer software or commercial computer software documentation. No additional government requirements beyond those set forth in the EULA shall apply, except to the extent that those terms, rights, or licenses are explicitly required from all providers of commercial computer software pursuant to the FAR and the DFARS and are set forth specifically in writing elsewhere in the EULA. Keysight shall be under no obligation to update, revise or otherwise modify the Software. With respect to any technical data as defined by FAR 2.101, pursuant to FAR 12.211 and 27.404.2 and DFARS 227.7102, the U.S. government acquires no greater than Limited Rights as defined in FAR 27.401 or DFAR 227.7103-5 (c), as applicable in any technical data.

## Warranty

THE MATERIAL CONTAINED IN THIS DOCUMENT IS PROVIDED "AS IS," AND IS SUBJECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. KEYSIGHT SHALL

NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFORMANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATERIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

## Safety Notices

## **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

## WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

## Contents

## 1 Introduction

|   | • 1 10                                                                                                                                                                                                                                 |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | <b>O</b> verview 10                                                                                                                                                                                                                    |

|   | First Edition (December 2020) 11 Second Edition (January 2021) 11 Third Edition (May 2021) 11 Fourth Edition (May 2022) 11 Fifth Edition (December 2023) 11                                                                            |

|   | <b>Support and Troubleshooting</b> 12                                                                                                                                                                                                  |

| 2 | ValiFrame HDMI Test Station                                                                                                                                                                                                            |

|   | ValiFrame HDMI Station Configuration 14  Test Station Configuration 15  Test Instrument Configuration 17                                                                                                                               |

|   | Starting the HDMI Station 19  FRL IP Auxiliary Files 21  Configuring the DUT 22  Configuration Parameters 23  Product Parameters 23  Test Parameters 24  Sink Test Configuration Parameters 25  Cable Test Configuration Parameters 27 |

| 3 | Using the Software                                                                                                                                                                                                                     |

|   | Introduction 32                                                                                                                                                                                                                        |

|                          | Selecting, Modifying, and Running Tests  Selecting Procedures 34  Modifying Parameters 34  Running Procedures 35             |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                          | <b>Required Calibration Data</b> 36                                                                                          |

|                          | Results 37                                                                                                                   |

|                          | Run-Time Data Display 37 Exporting Results 37                                                                                |

|                          | HDMI Parameters 39                                                                                                           |

|                          | Sequencer Parameters 39 Common Parameters 40 Procedure Parameters 40                                                         |

| 4 HDMI Sink Calibrations |                                                                                                                              |

|                          | <b>Overview</b> 42                                                                                                           |

|                          | Calibrations for Both Sinks and Cables 43 Skew Calibration 43 Fall/Rise Time Calibration 48                                  |

|                          | Sink Calibrations – HDMI 1.4 51  Swing Calibration 51  Clock Jitter Calibration 55  Data Jitter Calibration 59               |

|                          | Sink Calibrations – HDMI 2.1 TMDS 62  HF Swing Calibration 62  HF Clock Jitter Calibration 65  HF Data Jitter Calibration 69 |

|                          | Sink Calibrations – HDMI 2.1 FRL 72                                                                                          |

|                          | FRL Swing Calibration 72 Random Jitter Calibration 76 Eye Width Calibration 80 Eye Height Calibration 83                     |

#### 5 HDMI Cable Calibrations

Overview 88

#### Calibrations for Both Sinks and Cables 89

Skew Calibration 89

Fall/Rise Time Calibration 89

#### Cable Calibrations – HDMI 1.4 90

Swing Calibration 90

Data Jitter (on Clock) Calibration 91

#### Cable Calibrations – HDMI 2.1 TMDS 94

HF Swing Calibration 94

Data Jitter (on Clock) Calibration 6G 95

#### Cable Calibrations – HDMI 2.1 FRL 96

FRL Cable Swing Calibration 96

Random Jitter Calibration 99

Eye Width Calibration 101

Eye Height Calibration 102

FRL Cable Mode Conversion Swing Calibration 103

Mode Conversion Calibration 104

## 6 FRL Waveform Calculation

Calculate FRL Waveforms 108

Calculate HFR2-5 FRL Waveforms 109

#### 7 HDMI Receiver Tests for Sinks

**Overview** 112

HDMI ValiFrame Parameters 114

## HDMI 1.4 TMDS Signal 115

ID 8-5 Differential Swing 115

ID 8-6 Intra-Pair Skew 118

ID 8-7 Jitter Tolerance 121

## HDMI 2.1 TMDS Signal 124

ID HF2-1 Differential Swing 124

ID HF2-2 Intra-Pair Skew 126

ID HF2-51 Inter-Pair Screw 129

ID HF2-3 Jitter Tolerance 131

ID HF2-6 Video Timing 2160p 24bit 134

ID HF2-7 Video Timing 2160p Deep Color 136

ID HF2-8 Video Timing 2160p 3D 138

ID HF2-23 Pixel Decoding YCbCr 4:2:0 141

ID HF2-24 Pixel Decoding YCbCr 4:2:0 Deep Color 143

ID HF2-25 Sink Video Timing-21:9 (64:27) 145

ID HF2-36 Video Timing Non-2160p 24bit 148

ID HF2-37 Video Timing Non-2160p Deep Color 150

ID HF2-38 Video Timing Non-2160p 3D 152

## HDMI 2.1 FRL Signal 155

HFR2-1 Differential Swing Tolerance 155

HFR2-2 Intra-Pair Skew 158

HFR2-3 Inter-Pair Skew 161

HFR2-4 Minimum Link Rate 164

HFR2-5 Jitter Tolerance 167

| Additional Sink Tests in Expert Mode 170                            |

|---------------------------------------------------------------------|

| ID 8-15 Character Synchronization Test 170                          |

| ID 8-16 Acceptance of All Valid Packet Types 172                    |

| ID 8-19 Pixel Encoding Requirements 174                             |

| ID 8-20 Video Format Timing 176                                     |

| ID 8-21 Audio Clock Regeneration 178                                |

| ID 8-22 Audio Jitter Test 180                                       |

| ID 8-23 Audio Formats 182                                           |

| ID 8-24 Interoperability with DVI 184                               |

| ID 8-25 Deep Color 186                                              |

| ID 8-29: 3D Video Format Timing 188                                 |

| ID 8-30 4K x 2K Video Format Timing 190                             |

| ID 8-31 AVI InfoFrame supporting Extended Colorimetry, Content Type |

| and Selectable YCC Quantization Range 192                           |

| Differential Swing 194                                              |

Sink Inter-Pair Skew 197

Sensitivity to Jitter 199 HF: Intra-Pair Skew 202

Generic Video Format Timing 204

## Additional HDMI 2.1 FRL Signal Sink Tests in Expert Mode 206

Differential Swing Tolerance 206 FRL Error Pattern Check 209

Jitter Characterization Test 212

## 8 HDMI Receiver Tests for Cables

Overview 216

## Tests for Category 1 and 2 Cables 217

ID 5-3 Cable Eye Mask Measurement 217ID 5-5 Cable Inter-Pair Skew Measurement 220

## Tests for Category 3 (FRL) Cables 222

HFR7-1 DC Power Test 222

HFR7-21 Cable Eye Diagram 227

HFR7-22 Inter-Pair Skew 229

HFR7-23 Mode Conversion 231

## Cable Tests in Expert Mode 234

HF Cable Eye Mask Measurement 234

## 9 Appendix: HDMI Parameters

Overview 238

**Sequencer Parameters** 239

**HDMI PHY Common Parameters** 240

## **HDMI PHY Parameters for Individual Procedures** 241

HDMI PHY Parameters Used in All Individual Procedures 241

HDMI PHY Parameters for Individual Sink Calibrations 242

HDMI PHY Parameters for Individual Cable Calibrations 246

HDMI PHY Parameters for Individual Sink Tests 250

HDMI PHY Parameters for Individual Cable Tests 259

## 10 Appendix: Acronyms and Abbreviations

List of Acronyms 264

Keysight N5991HP1A HDMI 2.1 Receiver Compliance Test Automation Software

User Guide

# 1 Introduction

Overview / 10 Document History / 11 Support and Troubleshooting / 12

#### Overview

This guide provides a detailed description of the Keysight N5991 HDMI Test Automation Software Platform.

The BitifEye "ValiFrame" Test Automation software is globally marketed and supported by Keysight Technologies as N5991. This document describes the calibrations and test procedures conducted by N5991 ValiFrame for HDMI in detail.

The N5991 software implements compliance tests according to the requirements of the CTS for HDMI Version 1.4, the CTS for Sink Devices of HDMI Version 2.1, and the Generic CTS for Cat 3 Cables of HDMI Version 2.1. It also offers additional custom characterization tests to provide more details of the DUT behavior beyond the limits of compliance testing.

The ValiFrame HDMI Receiver Tests support automatic control of Keysight Technologies M8195A AWG. It calibrates the stress conditions and controls all test electronic equipment for automated receiver tolerance tests.

NOTE

The definitions of the acronyms and abbreviations used throughout this User Guide are given in Chapter 10, Appendix: Acronyms and Abbreviations.

## **Document History**

First Edition (December 2020)

The first edition of this user guide describes the functionality of software version N5991 ValiFrame HDMI\_1.0.

Second Edition (January 2021)

The second edition of this user guide describes the functionality of software version N5991 ValiFrame HDMI\_1.20 based on the HDMI Base specification.

Third Edition (May 2021)

The third edition of this user guide describes the functionality of software version N5991 ValiFrame HDMI\_1.2.4 based on the HDMI Base specification.

Fourth Edition (May 2022)

The fourth edition of this user guide describes the functionality of software version N5991 ValiFrame HDMI\_1.2.4 based on the HDMI Specification Version 2.1.

Fifth Edition (December 2023)

The fifth edition of this user guide describes the functionality of software version N5991 ValiFrame HDMI\_1.3.0 based on the HDMI Specification Version 2.1 (gCTS Revisions 1.4b and 2.1h).

## Support and Troubleshooting

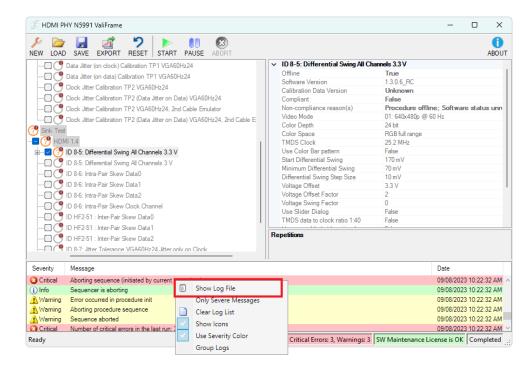

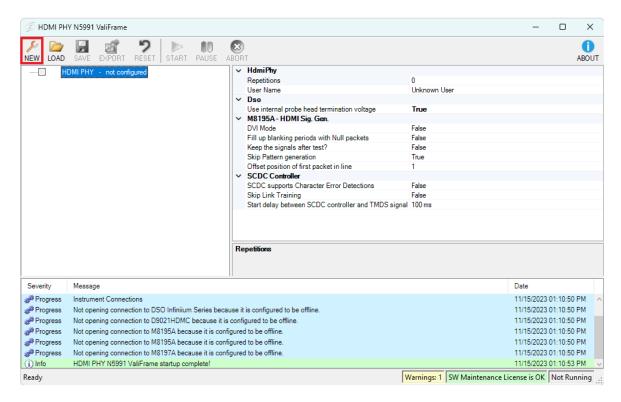

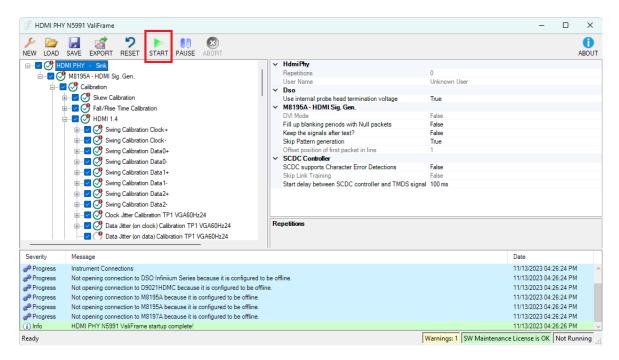

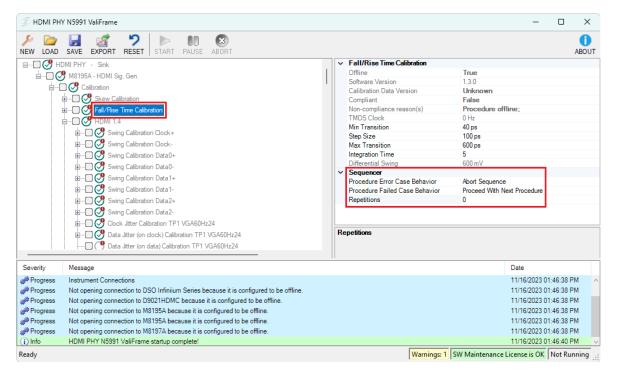

In case of problems when running the software, check the log list at the bottom of the main window. The log file can be viewed by right-clicking within the log list section (see red frame in Figure 1). The log file is temporarily saved at C:\ProgramData\BitifEye\ValiFrameK1\Tmp. Note that all log information will be lost when the N5991 application is terminated unless you save the log file.

Figure 1 Accessing the log file

If a problem with an application persists, send the log file with the problem to Keysight support.

The Keysight support team is also happy to help you should you require further information about a particular application.

For support options, visit www.keysight.com/find/contactus.

Keysight N5991HP1A HDMI 2.1 Receiver Compliance Test Automation Software

User Guide

# 2 ValiFrame HDMI Test Station

ValiFrame HDMI Station Configuration / 14 Starting the HDMI Station / 19

The test instruments that are together used for Test Automation are referred to as a Test Station. This chapter describes how to configure and start the N5991 ValiFrame HDMI Test Station.

## ValiFrame HDMI Station Configuration

The set of test instruments that are used for HDMI test automation are referred to in the following as the "Test Station" or simply "Station". The test station is controlled by a suitable PC and the N5991 Test Automation Software Platform.

First install the BitifEye N5991 ValiFrame HDMI software. Further details about this and the licenses required can be found in the N5991 Getting Started Guide.

The ValiFrame HDMI Station Configurator must be started prior to launching ValiFrame. It allows you to select the required set of instruments. Double-click the Station Configurator icon (see Figure 2) to launch the software. Alternatively, to access the Valiframe Station Configuration on a Windows 10-based PC, click

## Start > BitifEye HDMI PHY N5991 > HDMI PHY Station Configurator (N5991).

Figure 2 HDMI PHY Station Configurator icon

#### **Test Station Configuration**

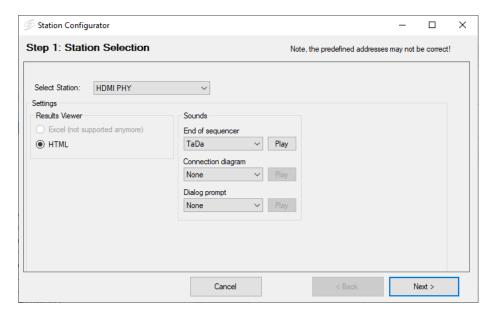

When the Valiframe HDMI PHY Station Configurator is launched, the first ValiFrame Station Configurator window appears as shown in Figure 3. The station is already selected as HDMI PHY.

Figure 3 Station Selection window

You may optionally assign sounds to mark different states of the program being reached.

- 1 **End of sequencer** plays the selected sound at the end of a sequence.

- 2 Connection diagram plays the selected sound every time a connection diagram pops up.

- 3 **Dialog prompt** plays the selected sound at each dialog prompt.

In each case, select a sound from the drop-down options. 'None' disables the sound for the respective action. Click **Play** to test a sound before assigning it to a specific action.

When you have finished, click **Next** to continue.

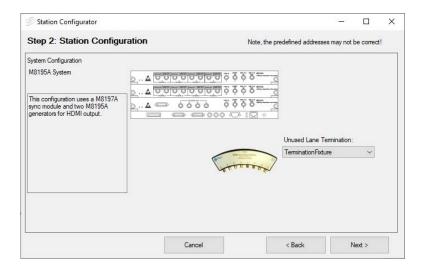

The Station Configuration stage of the Station Configurator is displayed in Figure 4. It shows the various options for instruments that can be used for HDMI testing. The options are described here.

Figure 4 Station Configuration Window

#### System Configuration

The 'System Configuration' part of the "Station Configuration" stage defines the HDMI signal generator. By default, 'M8195A system' is the signal generator available.

M8195A System. This configuration uses two M8195A generators for HDMI output and a M8197A synchronization module to de-skew the two M8195A modules.

#### **Unused Lane Termination**

Select an option as the method to terminate any unused lanes:

- Termination Fixture. Use a termination fixture.

- · Scope Probe. Use a scope probe such as

- N5444A/N280XA

- N5380A/B

#### Test Instrument Configuration

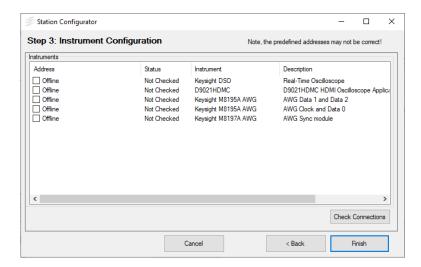

Once the HDMI station is configured, the instrument addresses must be set. An example for instrument configuration is shown in Figure 5.

Figure 5 Instrument Configuration Window

NOTE

Make sure that all the selected instruments for the test station are connected to the test station PC controller by remote control interfaces such as LAN or USB.

After the installation process, all instruments are configured by default in "Offline" mode. In this simulation mode, hardware does not need to be physically connected to the test controller PC. The ValiFrame software cannot connect to any instrument in this mode. In order to control the instruments that are connected to the PC, the instrument address must be entered. The address depends on the bus type used for the connection, for example, LAN or USB.

Most of the instruments used in the HDMI station require a VISA connection. To determine the VISA address, run the "Keysight Connection Expert", which is part of the Keysight IO Libraries Suite. Either right-click the Keysight IO Control icon in the task bar and select the first entry "Connection Expert" or select "Keysight Connection Expert" directly from

the list of programs. For each instrument, copy the address string from the Connection Expert entries and paste it as the instrument address in the ValiFrame Station Configurator.

For further details about how to use the Keysight Connection Expert, see the N5991 Getting Started Guide.

After the address strings have been entered, click **Check Connections** to verify that the connections for the instruments are established properly. If anything is wrong in the instrument address, the Configurator displays a prompt to indicate so.

Click **Finish** to save the changes and close the ValiFrame Station Configurator.

## NOTE

When starting a specific test station configuration for the first time, all instruments are set to the "Offline" mode. In this mode the test automation software does not connect to any instrument. This mode can be used for demonstrations or checks only. NO VALID DATA IS PRODUCED.

## Starting the HDMI Station

Start the Valiframe HDMI Test Station by double-clicking the **HDMI PHY Valiframe (N5991)** icon on the desktop as shown in Figure 6. Alternatively, for a PC running Windows 10, start the Valiframe HDMI station from **Start / BitifEye HDMI PHY N5991 / HDMI PHY ValiFrame (N5991)**.

Figure 6 HDMI PHY ValiFrame (N5991) icon

The ValiFrame N5991 connects automatically to the instruments that are set to "Online" mode in the ValiFrame Instrument Configuration (see Figure 5). The application is ready for use once all the connections have been initialized successfully. Clicking the ValiFrame HDMI icon launches the N5991 Test Automation Software Platform window as shown in Figure 7.

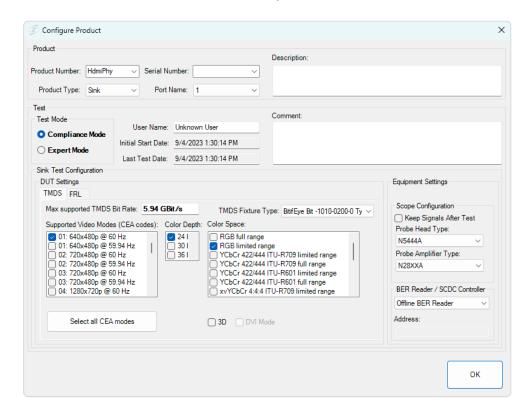

The test parameters must be configured before you run any test or calibration procedure. Click **NEW** (red frame in Figure 7) to open the "Configure Product" window (Figure 9).

Figure 7 ValiFrame HDMI user interface

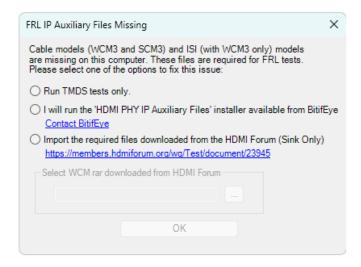

#### FRL IP Auxiliary Files

When you launch the ValiFrame Station for the first time, a dialog prompting for FRL IP Auxiliary files appears (see Figure 8). Note that FRL cable tests are available only if the WCM and PCB loss models are located on the same machine as the ValiFrame software. These files can be added by using the HDMI IP Auxiliary installer (provided by BitifEye) or by downloading them from the HDMI Forum.

Figure 8 FRL IP Auxiliary dialog

#### Configuring the DUT

The "Configure Product" window (Figure 9) allows you to select the DUT parameters, such as Product Type and Test Mode (either Compliance Mode or Expert Mode), but also other parameters that are related to the Sink/Cable test configuration. These parameters will be used later in several calibrations and test procedures.

Figure 9 Configure Product panel for product type 'Sink'

#### Configuration Parameters

The names and descriptions of parameters that appear in the "Configure Product" window are divided up in the Configure Product panel as follows:

- Product Parameters (Table 1 on page 23)

- Test Parameters (Table 2 on page 24)

- Test Mode

- Sink Test Configuration Parameters (for Product Type "Sink")

- DUT Settings

- TMDS (Table 3 on page 25)

- FRL (Table 4 on page 26)

- Equipment Settings

- Scope Configuration

- BER Reader / SCDC Controller

- Cable Test Configuration Parameters (for Product Type "Cable")

- Cable DUT Settings

- Equipment Settings

- Scope Configuration

These parameters are described in more detail in the following sections.

#### **Product Parameters**

The product parameters, which give details of the product (DUT), are listed and described in Table 1.

Table 1 Product parameters

| Parameter name | Description                                                                                                                                            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Number | Name of the product (set as HDMI PHY).                                                                                                                 |

| Serial Number  | Serial number of the product.                                                                                                                          |

| Product Type   | The available product types are 'Sink' and 'Cable'. The list of calibrations and tests in the procedure tree will vary according to the type selected. |

| Port Name      | Select a port number between 1 and 10.                                                                                                                 |

| Description    | Text field to describe the product.                                                                                                                    |

#### Test Parameters

The test parameters, which give details of the test situation, are considered in the following sections. First, the general parameters are listed and described in Table 2.

Table 2 Test Parameters (general)

| Parameter name     | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| User Name          | User name text field.                                                                                                                                                                                                                                                                                                                                                                                |

| Comment            | Text file for user comments.                                                                                                                                                                                                                                                                                                                                                                         |

| Initial Start Date | Time stamp of the start of the current session.                                                                                                                                                                                                                                                                                                                                                      |

| Last Test Date     | Time stamp of the last test conducted in the current session.                                                                                                                                                                                                                                                                                                                                        |

| Test Mode          | <ul> <li>Compliance Mode: Tests are conducted as mandated by the CTS. The parameters that are shown in the calibrations and test procedures cannot be modified by the user.</li> <li>Expert Mode: Calibration and tests can be conducted beyond the limits and constraints of the CTS. The parameters that are shown in the calibrations and test procedures can be modified by the user.</li> </ul> |

#### Sink Test Configuration Parameters

This section describes the parameters to configure a sink test. An example configuration is shown in the lower half of Figure 9 on page 22.

#### **DUT Settings**

The DUT Settings for sink test configuration are further divided into two sections: those for 'TMDS' testing (Table 3) and those for 'FRL' testing (Table 4), which have different "tabs" in the Configure Product panel.

Table 3 Sink Test Configuration Parameters (for TMDS)

| TMDS Parameter Name               | Description                                                                                                                                                                                                                                                                      |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Max supported TMDS Bit Rate       | This parameter enables the test list to be filtered with respect to the maximum TMDS bit rate supported by the DUT. The list of test procedures will only include video mode, color depth and color space combinations with a TMDS bit rate equal to or below the entered value. |

| TMDS Fixture Type                 | Select different fixture types for the oscilloscope measurements where the fixture can be de-embedded. The options are:  High Z Probe  Wilder HDMI TPA-P  BitifEye BIT-1010-0200-0 Type A  Other                                                                                 |

| Supported Video Modes (CEA codes) | Select one or more video modes supported by the DUT.                                                                                                                                                                                                                             |

| Color Depth                       | Select one or more color depth options supported by the DUT.                                                                                                                                                                                                                     |

| Color Space                       | Select one or more pixel-encoding options supported by the DUT.                                                                                                                                                                                                                  |

| Select all CEA modes              | Selecting this option enables all standard CEA video modes.                                                                                                                                                                                                                      |

| 3D                                | Selecting this option adds 3-dimensional video modes to the test procedures.                                                                                                                                                                                                     |

| DVI Mode                          | Selecting this option enables DVI compatibility. Available only in Expert Mode.                                                                                                                                                                                                  |

Table 4 Sink Test Configuration Parameters (for FRL)

| FRL Parameter name      | Description                                                                                                                                                               |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRL Test Patterns       | Select the pattern used for sink tests.                                                                                                                                   |

| Max supported FRL Lanes | Select the maximum number of FRL lanes supported by the DUT.                                                                                                              |

| Max supported FRL Rate  | This parameter enables the test procedure list to be filtered with respect to the maximum FRL bit rate supported by the DUT.                                              |

| FRL Fixture Type        | Select different fixture types for the oscilloscope measurements where the fixture can be de-embedded. The options are:  BitifEye 2.1 TPA Wilder 2.1 TPA Luxshare 2.1 TPA |

## **Equipment Settings**

Table 5 gives the Equipment Settings available for sink test configuration.

Table 5 Sink Test Configuration Parameters (Equipment Settings)

| Parameter name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keep Signals After Test      | When this option is checked, the software allows you to pause and keep signal outputs active between test procedures so that signals can be checked after a test has been run with the DUT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Probe Head Type              | Select the probe head for the oscilloscope measurements. The options are:  None  N5444A  N5380A/B (only in Expert Mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Probe Amplifier Type         | Select the amplifier for the oscilloscope measurements. The options are:  N28XXA N7010A N7003A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

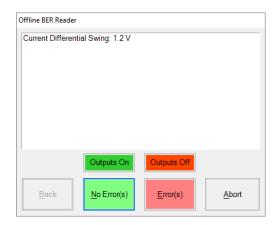

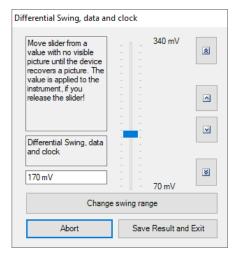

| BER Reader / SCDC Controller | <ul> <li>This parameter includes a BER Reader to improve test automation. You may also use an HDMI SCDC Controller to set HDMI 2.1 SCDC bits automatically and use the bit error ratio reading capability.</li> <li>HDMI SCDC Controller/Allion SCDC Controller. Select one of these options if an SCDC Controller should be used for SCDC bits. Optionally, it can be configured to read character errors automatically. The SCDC Controller can be connected directly to the PC running ValiFrame via USB or to a remote PC running the BitifEye Remote Instruments Server. If there is a direct connection, leave the 'Address' field blank. Otherwise you must enter the Host IP address for the BitifEye Remote Instruments Server.</li> <li>If no BER Reader is available, select the option 'Offline BER Reader'. ValiFrame will then use dialog boxes to guide you through setting SCDC bits and checking for errors during the tests. This option is only available for TMDS tests. If 'Offline BER Reader' is selected, HDMI 2.1 - FRL tests are not available.</li> </ul> |

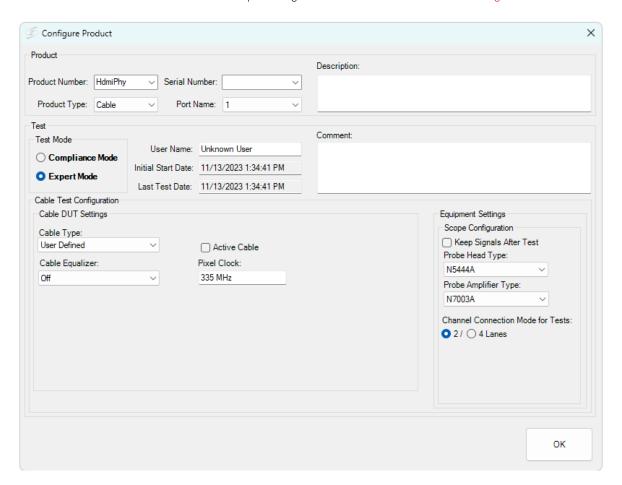

#### Cable Test Configuration Parameters

This section describes the parameters to configure a cable test. An example configuration is shown in the lower half of Figure 10.

Figure 10 Configure Product panel for product type 'Cable'

NOTE

FRL cable tests are available only if the WCM and PCB loss models are located on the same machine as the ValiFrame software. See FRL IP Auxiliary Files on page 21.

## Cable DUT Settings

Table 6 describes the cable test configuration parameters found under cable DUT settings.

Table 6 Cable Test Configuration Parameters (Cable DUT Settings)

| Parameter name           | Description                                                                                                                                                                                                |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cable type               | Select the category of the DUT. The options are:  Category 1 (Home)  Category 2 (Home)  Category 3 (FRL)  User Defined                                                                                     |

| Active cable             | Select this check box if the connected DUT is of the 'active cable' type.                                                                                                                                  |

| Cable Equalizer          | Available only for Cable Types 'Category 2 (Home)' and 'User Defined' and only in Expert Mode. Select as Off 2 m Cable Equalizer 5 m Cable Equalizer 10 m Cable Equalizer                                  |

| Max. Supported FRL Lanes | Available only for Cable Type 'Category 3 (FRL)' and only in Expert Mode.  Select the maximum number of supported data lanes as:  3 Data Lanes  4 Data Lanes                                               |

| Max. Supported FRL Rate  | Available only for Cable Type 'Category 3 (FRL)' and only in Expert Mode.  Select the maximum supported data rate as:  3 Gb/s  6 Gb/s  8 Gb/s  10 Gb/s  12 Gb/s                                            |

| FRL Fixture Type         | Available only for Cable Type 'Category 3 (FRL)'.  Select the fixture type:  BitifEye 2.1 TPA  Wilder 2.1 TPA  Luxshare 2.1 TPA  (Only for User Defined type): Set the pixel clock rate of the cable here. |

| Pixel Clock              | Available only for Cable Type 'User Defined', which is only available in Expert Mode. Set the pixel clock rate of the cable here.                                                                          |

## **Equipment Settings**

The Equipment Settings available for cable test configuration are described in Table 7.

Table 7 Cable Test Configuration Parameters (Equipment Settings)

| Parameter name                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keep Signals After Test          | When this option is checked, the software allows you to pause and keep signal outputs active between test procedures so that signals can be checked after a test has been run with the DUT.                                                                                                                                                                                                                                        |

| Probe Head Type                  | Select different probe heads for the oscilloscope measurements. The options are:  None  N5444A  N5380A/B (only in Expert Mode)                                                                                                                                                                                                                                                                                                     |

| Probe Amplifier Type             | Select different probe amplifiers for the oscilloscope measurements. The options are:  N28XXA N7010A N7003A                                                                                                                                                                                                                                                                                                                        |

| Channel Connection Mode for Test | This parameter allows you to select the number of connections required for oscilloscope measurements. The available choices depend on the oscilloscope and may include  2 Lanes 4 Lanes If the accessories for a 4-connection setup are available and the generator does not have any limitations, the 4-connection setup should be chosen as this has the advantage that most of the tests can be run without altering the setup. |

2 ValiFrame HDMI Test Station

# Keysight N5991HP1A HDMI 2.1 Receiver Compliance Test Automation Software

User Guide

# 3 Using the Software

Introduction / 32

Selecting, Modifying, and Running Tests / 34

Required Calibration Data / 36

Results / 37

HDMI Parameters / 39

This chapter describes how to select the calibrations and test procedures that are to be run and how you can modify the parameters in expert mode — if required — to go beyond the tests specified by the CTS.

#### Introduction

Once the DUT has been configured, click 'OK' in the "Configure Product" panel. All calibration and test procedures are included in the respective groups in a manner similar to how they are organized in the specifications.

Figure 11 HDMI main window

The **parameter grid** on the right side of the window shows the parameters that are related to the individual procedure or group of procedures selected on the left.

The **log list** in the bottom pane of the window shows calibration and test status messages (regular progress updates as well as warnings and error messages).

The **status bar** at the very bottom provides information about how many critical errors have occurred, how many warnings have been sent, the status of the software maintenance license and whether ValiFrame is running.

To start one or more procedures, select the corresponding check box(es). Then the 'Start' button is enabled and turns green (outlined in red in Figure 11). Click Start to run the selected procedure(s).

Once all the procedures have been run, the N5991 configuration can be stored as a single '.vfp' file using the 'Save' button and recalled using the 'Load' button without the need to configure the DUT again.

## **CAUTION**

Before executing the calibration or test procedures, ensure that the HDMI Station Configuration is conducted properly with all necessary instruments, such as the Infiniium oscilloscope, set to "online". All calibrations can be run in offline mode, that is, without any instrument connected. The offline mode is intended for product demonstrations with simulated data. CALIBRATIONS RUN IN OFFLINE MODE DO NOT GENERATE VALID CALIBRATION DATA.

## NOTE

If you have already performed calibrations and tests, when you update ValiFrame and open it, you may see several log messages saying that the measurements are not compliant. This is because ValiFrame now records the exact setup and software version used for the calibrations and, even if your setup has not changed, the information required by ValiFrame to categorize the results as compliant is not available. Compliance information is also available in the result report of each procedure.

## Selecting, Modifying, and Running Tests

#### Selecting Procedures

The calibration and receiver test procedure groups can be selected globally by clicking the check box at the top of the group. Alternatively, an individual test procedure can be selected by checking the corresponding check box. Click 'Start' to run the selected test procedures.

## NOTE

Procedures available only in Expert Mode, that is, those that are not required for compliance, are listed in the procedure tree in a separate group "Expert Mode" after the groups HDMI 1.4, HDMI 2.1 – TMDS and HDMI 2.1 - FRL for sink DUTs and after the groups Cable Tests – Data and Cable Tests – Clock for cable DUTs (categories 1 and 2).

#### Modifying Parameters

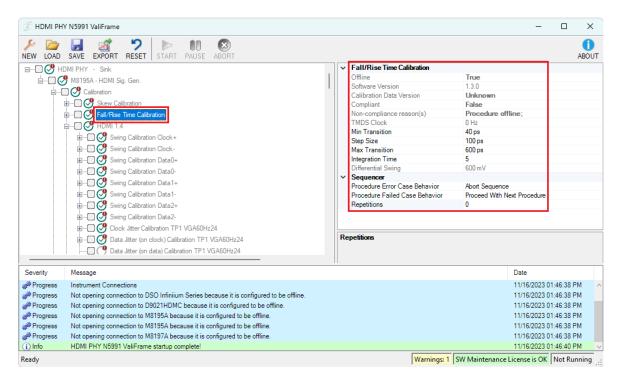

Most calibration and test procedures as well as the groups containing them have parameters that control the details of how the procedures are run. In compliance mode, most of these parameters are read-only. In expert mode, almost all the parameters can be modified. First, select a specific calibration or test procedure or one of the groups contained in the N5991 procedure tree as shown in Figure 12. The parameters are displayed in a property list (parameter grid) on the right side of the window. These parameters can be configured only before the selected procedure subgroup or procedure is started. All of the selected test parameters are listed in the test results.

Figure 12 Modifying parameters in the HDMI PHY N5991 ValiFrame main window

#### Running Procedures

To run the selected procedure, click the **Start** button on the toolbar (see Figure 12). The procedures are run sequentially in the order shown in the procedure selection tree. Some procedures may require user intervention, such as changing cable connections or entering DUT parameters. The required action is prompted in pop-up dialog boxes before the calibration/test procedures are run.

To view the connection diagram, right-click the desired test or calibration. From the right-click menu, select "Show Connection...".

The status of each procedure is indicated by the round icon next to its name in the procedure tree. For more details about the meanings of the icons, see the N5991 Getting Started Guide, which can be downloaded from the BitifEye homepage.

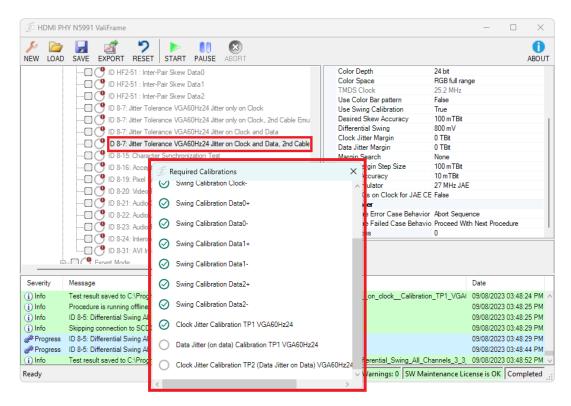

## Required Calibration Data

Some of the calibration procedures and most of the test procedures require calibration data that has been measured previously. You can see the calibration data required by a particular procedure by right clicking its name in the procedure tree and selecting 'Required Calibrations'. A list of the prerequisite calibrations drops down (Figure 13).

Figure 13 Example list of required calibrations

The icon next to the name of a calibration procedure in the list indicates whether the calibration has been run successfully (green), is incomplete (yellow), failed (red) or has not yet been run (gray).

## Results

## Run-Time Data Display

Most procedures generate data output. While the procedure is running, the data is displayed in a results window, which opens automatically for each individual procedure.

Any results windows that are open during the procedure runs are closed automatically once the specific procedure is finished. As long as the N5991 Software is running, each result file can be reopened by double-clicking the respective procedure. However, the individual files are lost when the N5991 main window is closed, unless you save the individual files or a collection of them

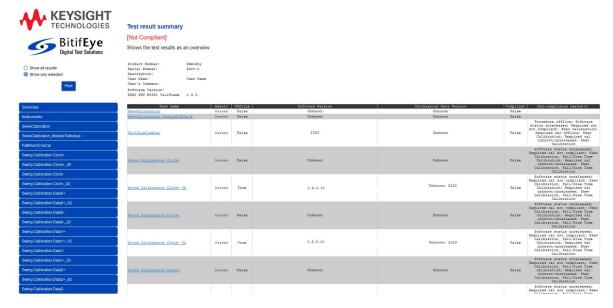

## **Exporting Results**

For your convenience, all individual results are summarized in an HTML document at the end of the test run (see Figure 14 on page 38). All calibration and test data worksheets can be saved in a workbook by clicking the **Export** button on the toolbar of the HDMI PHY N5991 ValiFrame main window. Keysight recommends performing this action at least at the end of each HDMI PHY N5991 ValiFrame procedure run to avoid any data loss. If the calibration and test procedures are conducted several times during the same HDMI PHY N5991 ValiFrame run, the resulting worksheets are combined in a workbook. If a test procedure is conducted without prior execution of calibration procedures in the same test run, only the test results will be saved to the workbook.

# NOTE

As a safety feature, all calibration and test results are saved by default to the N5991 "Tmp" directory (C:\ProgramData\BitifEye\ValiframeK1\Tmp). The sub-folder "Results\HdmiPhy Station" contains the HTML files of the final results measured at each calibration and test procedure.

In addition to the calibration data HTML files, calibration data files are generated. These files are saved by default to the N5991 calibrations folder 'C:\ ProgramData\BitifEye\ValiframeK1\HdmiPhy\Calibrations'. If these calibrations are run again, the data file is overwritten. To save the calibration data files at each configuration, the files must be copied from this folder and saved manually in a different folder before the calibrations are rerun.

Figure 14 Example summary page (just the top) of an HDMI PHY N5991 ValiFrame workbook

## **HDMI** Parameters

The HDMI parameters are of three types:

- · Sequencer Parameters

- · Common Parameters

- Procedure Parameters

## Sequencer Parameters

The sequencer parameters control the flow of the test sequencer only, not the behavior of individual procedures. One of them, Repetitions, is available for all procedures and groups in the procedure tree. The others are only available for procedures. Like all other parameters, the sequencer parameters are shown in the right half of the ValiFrame user interface and you may manually change them, as illustrated in Figure 15.

Figure 15 HDMI sequencer parameters

All sequencer parameters are listed in alphabetical order in Table 8 on page 239.

#### Common Parameters

The common parameters are used for several related calibration or test procedures. They are shown on the right side of the ValiFrame user interface when the selected entry of the procedure tree on the left is a group instead of an individual procedure.

The HDMI Receiver Test Software has some group parameters (in addition to "Repetitions") on the top-level entry of the HDMI procedure tree. These are common for all Valiframe HDMI PHY calibration and receiver test procedures.

All of the common parameters are listed in Table 9 on page 240 in the order they appear in the user interface.

#### Procedure Parameters

The Procedure Parameters are all such parameters that are not part of any of the previously described categories. They are shown on the right side of the ValiFrame user interface when the selected entry of the procedure tree on the left is an individual procedure. Their purpose is to modify the behavior of that single procedure. Procedures often have parameters with the same name, but pre-configured settings always apply to the selected procedure, while their meaning may be slightly different.

The procedure parameters are listed alphabetically in

- Table 10 on page 241 (parameters used in all procedures)

- Table 11 on page 242 (parameters for sink calibrations)

- Table 12 on page 246 (parameters for cable calibrations)

- Table 13 on page 250 (parameters for sink tests)

- Table 14 on page 259 (parameters for cable tests)

Keysight N5991HP1A HDMI 2.1 Receiver Compliance Test Automation Software

User Guide

# 4 HDMI Sink Calibrations

Overview / 42

Calibrations for Both Sinks and Cables / 43

Sink Calibrations - HDMI 1.4 / 51

Sink Calibrations - HDMI 2.1 TMDS / 62

Sink Calibrations – HDMI 2.1 FRL / 72

Before any sink or cable test procedure can be run, the HDMI PHY test system must be calibrated. The procedures used for a sink DUT are described in this chapter.

## Overview

The purpose of the calibration procedures is to calibrate the TDMS and FRL signal generator levels and timings.

ValiFrame automatically determines the required calibration procedures according to the parameters set in the Configure Product dialog, including

- Product Type (sink or cable)

- Test Mode (compliance or expert)

- TMDS or FRL

- · Supported Video Modes

- · Color Depth

- · Color Space

- · Cable Type

The results of each calibration are stored in the 'Calibration' folder of ValiFrame, so that they can be used for another calibration or test, as required.

The order of the procedures in the procedure tree is driven mainly by the calibration dependencies.

For calibrations, in general, the following calibrations are prerequisite:

- · The appropriate skew calibration.

- All the calibrations listed above it in the same branch of the procedure tree.

They are not listed explicitly for each calibration in this User Guide. However, they can be found directly in the application (see Required Calibration Data on page 36 of this User Guide).

Note that ValiFrame attempts to reduce the calibration effort by coalescing similar data rates into one calibration, when no significant deviation in the results is expected.

DC and single-ended levels are always determined with respect to the termination voltage.

## Calibrations for Both Sinks and Cables

Skew Calibration

## Purpose and Method

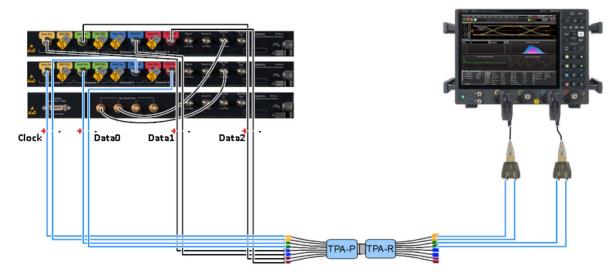

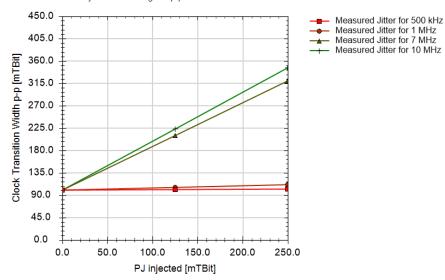

This calibration is used to de-skew the setup. Because of the differences in length between Clock, Data0, Data1 and Data2, the output signals are not aligned on the same base. Additionally, this calibration performs the module alignment of the two M8195A modules using the M8197A synchronization module.

The length differences are measured in several steps and finally saved in a calibration table. With additional steps, the software measures the module-to-module skew for specific sample frequencies and saves this in a calibration table as well. For each test, this data table is used to de-skew the signals.

## Connection Diagram

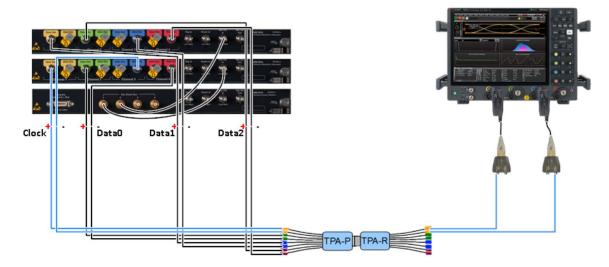

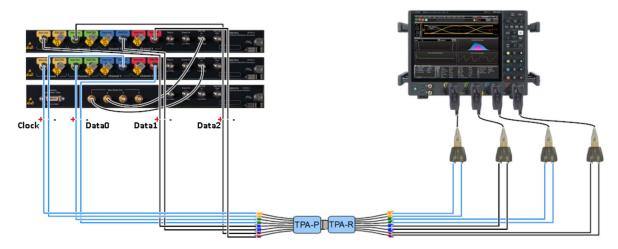

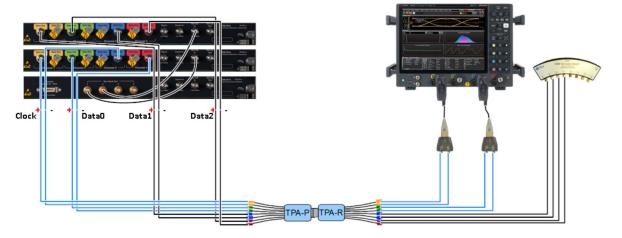

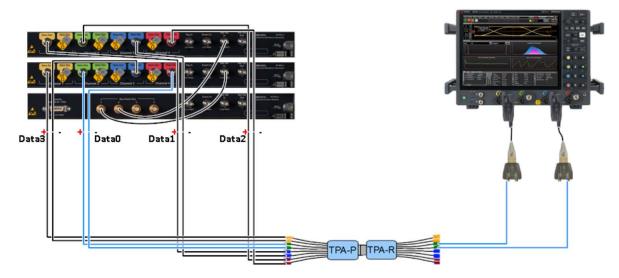

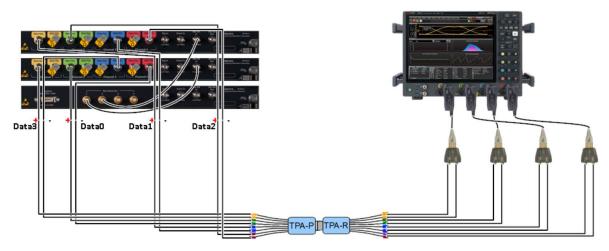

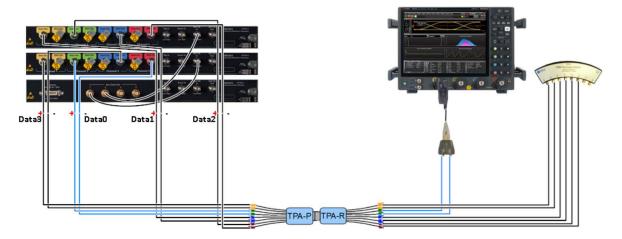

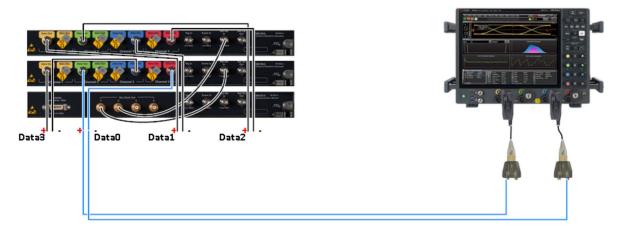

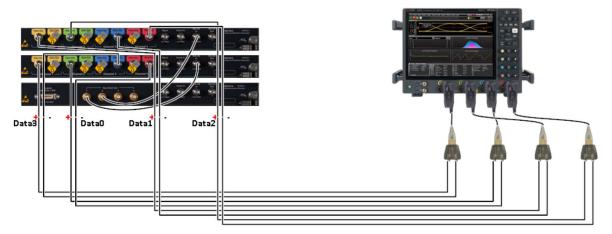

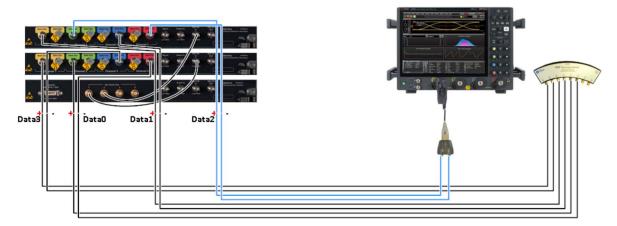

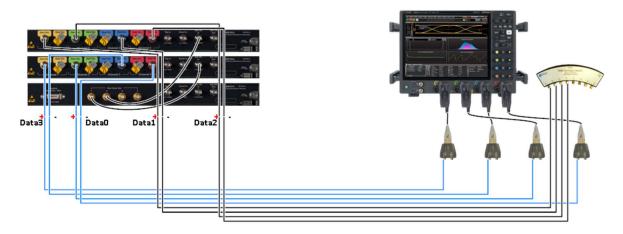

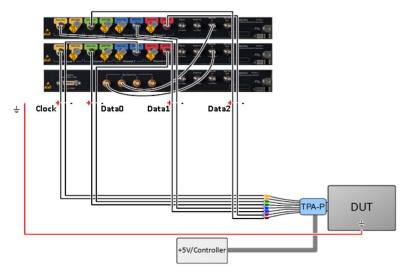

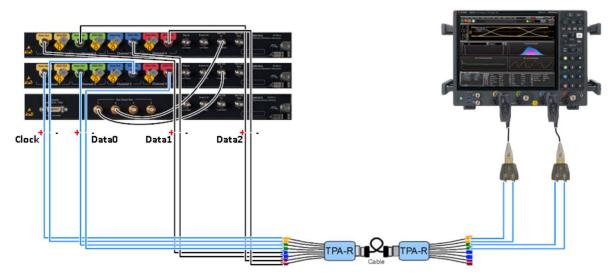

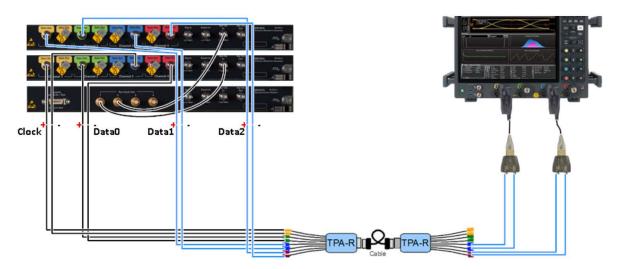

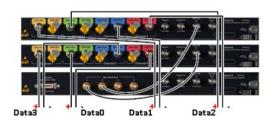

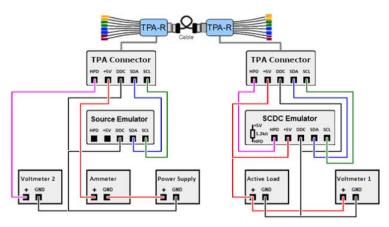

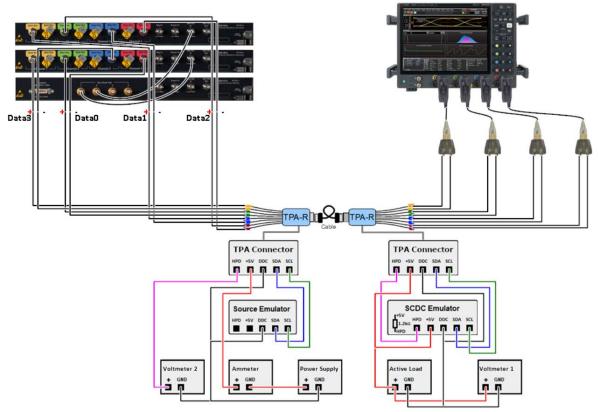

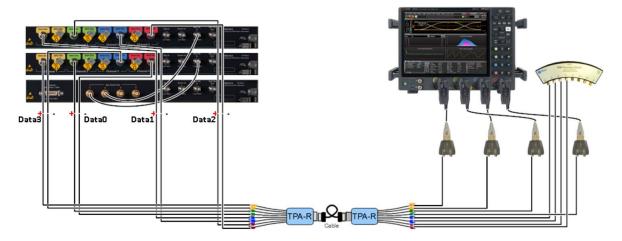

During the test, the software prompts you to change the outputs connected to the oscilloscope. Initially, M8195A module 1 outputs (Clock and Data0) must be connected. Thereafter, these must be replaced with M8195A module 2 outputs (Data1 and Data2). Finally, to calibrate the module-to-module skew, you must connect both modules 1 and 2 to the oscilloscope. See Figure 16, Figure 17 and Figure 18.

Figure 16 Example connection diagram for Sink Skew Calibration (connection 1)

Figure 17 Example connection diagram for Sink Skew Calibration (connection 2)

Figure 18 Example connection diagram for Sink Skew Calibration (connection 3)

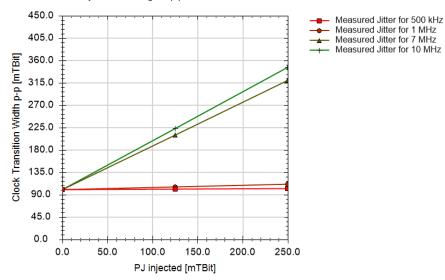

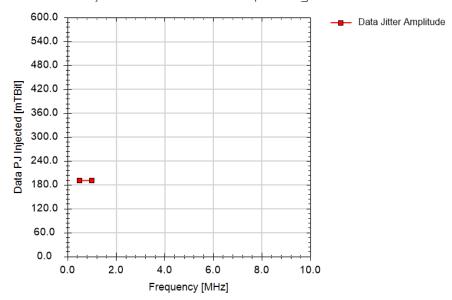

The example result in Figure 19 shows the calibration data used to de-skew the setup.

The second page of results gives the module-to-module skew for various frequencies set on the AWG (Figure 20).

## **Skew Calibration**

## [Not Compliant]

#### Skew Calibration

| General                                             |                                         |

|-----------------------------------------------------|-----------------------------------------|

| Offline                                             | True                                    |

| Software Version                                    | 1.3.0                                   |

| Compliant                                           | False                                   |

| Non-compliance reason(s)                            | Procedure offline; Software status unre |

| Step size of sample frequency                       | 250 MHz                                 |

| User Name                                           | Unknown User                            |

| M8195A - HDMI Sig. Gen                              |                                         |

| DVI Mode                                            | False                                   |

| Fill up blanking periods with Null packets          | False                                   |

| Keep the signals after test?                        | False                                   |

| Skip Pattern generation                             | True                                    |

| SCDC Controller                                     |                                         |

| SCDC supports Character Error Detections            | False                                   |

| Skip Link Training                                  | False                                   |

| Start delay between SCDC controller and TMDS signal | 100 ms                                  |

| Dso                                                 |                                         |

| Use internal probe head termination voltage         | True                                    |

|                                                     |                                         |

| Result | Identifier             | [ns]  |

|--------|------------------------|-------|

| pass   | AWG1.CH1+ to AWG1.Ch2+ | 0.002 |

| pass   | AWG1.CH1+ to AWG1.Ch3- | 0.003 |

| pass   | AWG1.CH1+ to AWG1.Ch4- | 0.002 |

| pass   | AWG2.CH1+ to AWG2.Ch2+ | 0.003 |

| pass   | AWG2.CH1+ to AWG2.Ch3- | 0.004 |

| pass   | AWG2.CH1+ to AWG2.Ch4- | 0.005 |

Figure 19 Example result for Skew Calibration

- Result: (Pass/Fail) Test is considered as passed if the measured skew is below the maximum limits.

- Identifier: The skew is measured between these M8195A outputs.

- · Skew Value [ns]: Measured skew value for each output

# SkewCalibration\_ModuleToModule

## [Not Compliant]

Calibrates the module to module skew

| General                                             |                                |

|-----------------------------------------------------|--------------------------------|

| Offline                                             | True                           |

| Software Version                                    | 1.3.0                          |

| Compliant                                           | False                          |

| Non-compliance reason(s)                            | Procedure offline; Software st |

| Step size of sample frequency                       | 250 MHz                        |

| User Name                                           | Unknown User                   |

| M8195A - HDMI Sig. Gen                              |                                |

| DVI Mode                                            | False                          |

| Fill up blanking periods with Null packets          | False                          |

| Keep the signals after test?                        | False                          |

| Skip Pattern generation                             | True                           |

| SCDC Controller                                     |                                |

| SCDC supports Character Error Detections            | False                          |

| Skip Link Training                                  | False                          |

| Start delay between SCDC controller and TMDS signal | 100 ms                         |

| Dso                                                 |                                |

| Use internal probe head termination voltage         | True                           |

| Result | Sample<br>Frequency<br>[GHz] | Skew Value<br>[ps] |

|--------|------------------------------|--------------------|

| pass   | 53.760                       | -12.0              |

| pass   | 54.010                       | -13.7              |

| pass   | 54.260                       | -15.2              |

| pass   | 54.510                       | -16.6              |

| pass   | 54.760                       | -17.7              |

| pass   | 55.010                       | -18.6              |

| pass   | 55.260                       | -19.3              |

| pass   | 55.510                       | -19.8              |

| pass   | 55.760                       | -20.0              |

| pass   | 56.010                       | -19.9              |

| pass   | 56.260                       | -19.7              |

| pass   | 56.510                       | -19.1              |

| pass   | 56.760                       | -18.4              |

| pass   | 57.010                       | -17.4              |

| pass   | 57.260                       | -16.2              |

| pass   | 57.510                       | -14.8              |

| pass   | 57.760                       | -13.2              |

| pass   | 58.010                       | -11.4              |

| pass   | 58.260                       | -9.6               |

| pass   | 58.510                       | -7.5               |

| pass   | 58.760                       | -5.4               |

| 22.55  | 59 010                       | -0 0               |

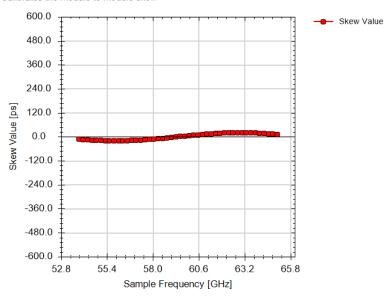

Figure 20 Example result for Skew Calibration (module-to-module). Just the top of the table

- Result: (Pass/Fail) Test is considered as passed if the measured skew is below the maximum limits.

- · Sample Frequency: The M8195A sample frequency that has been set.

- Skew Value: Measured skew value between the M8195A modules for each sample frequency.

#### Fall/Rise Time Calibration

## Purpose and Method

Transition times can be created on an M8195A by manipulating waveforms instead of using hardware TTCs. Test fixtures and cables affect the transition times. To compensate for this, the fall and rise times are calibrated by generating a clock signal and measuring the rise time with a DSO.

For the calibration, a valid clock signal of the lowest video mode is generated with different transition times. For each step, the DSO measures the rise time of the signal and averages the measured transition time over multiple measurements.

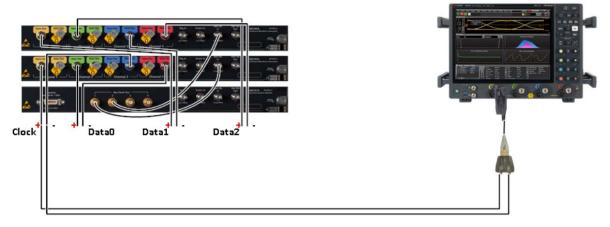

## Connection Diagram

See Figure 21.

Figure 21 Example connection diagram for Fall/Rise Time Calibration – M8195A setup

NOTE

This connection diagram is specifically for the N5444A/N28XXA probe head. If a different probe head is selected in the Configure DUT dialog, the connection diagram will be slightly different.

#### FallRiseTimeCal

## [Not Compliant]

Calibrates the transition time

| General                                    |                                                                                                                                                                                                 |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offline                                    | True                                                                                                                                                                                            |

| Software Version                           | 1.3.0.9_RC                                                                                                                                                                                      |

| Calibration Data Version                   | Unknown                                                                                                                                                                                         |

| Compliant                                  | False                                                                                                                                                                                           |

| Non-compliance reason(s)                   | Procedure offline; Software status unreleased; Required cal<br>not compliant: Skew Calibration; Required cal offline: Skew<br>Calibration; Required cal unknown/unreleased: Skew<br>Calibration |

| Video Mode                                 | 64: 1920x1080p @ 100 Hz                                                                                                                                                                         |

| Color Depth                                | 24 bit                                                                                                                                                                                          |

| Color Space                                | RGB full range                                                                                                                                                                                  |

| Use Color Bar pattern                      | False                                                                                                                                                                                           |

| Min Transition                             | 40 ps                                                                                                                                                                                           |

| Step Size                                  | 100 ps                                                                                                                                                                                          |

| Max Transition                             | 600 ps                                                                                                                                                                                          |

| Integration Time                           | 5                                                                                                                                                                                               |

| User Name                                  | Unknown User                                                                                                                                                                                    |

| M8195A - HDMI Sig. Gen                     |                                                                                                                                                                                                 |

| DVI Mode                                   | False                                                                                                                                                                                           |

| Fill up blanking periods with Null packets | False                                                                                                                                                                                           |

| Keep the signals after test?               | False                                                                                                                                                                                           |

| Skip Pattern generation                    | True                                                                                                                                                                                            |

#### 4 HDMI Sink Calibrations

| Set<br>Fall/Rise<br>Time [ps] | Measured<br>Fall/Rise<br>Time at 27<br>[ps] | Measured<br>Fall/Rise<br>Time at 74<br>[ps] | Measured<br>Fall/Rise<br>Time at 148<br>[ps] | Measured<br>Fall/Rise<br>Time at 165<br>[ps] | Measured<br>Fall/Rise<br>Time at 223<br>[ps] | Measured<br>Fall/Rise<br>Time at 297<br>[ps] | Measured<br>Fall/Rise<br>Time at 340<br>[ps] | Measured<br>Fall/Rise<br>Time at 594<br>[ps] |

|-------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| 600.0                         | 331                                         | 379                                         | 393                                          | 396                                          | 400                                          | 403                                          | 405                                          | 408                                          |

| 500.0                         | 277                                         | 317                                         | 330                                          | 332                                          | 335                                          | 338                                          | 340                                          | 343                                          |

| 400.0                         | 224                                         | 256                                         | 266                                          | 268                                          | 271                                          | 274                                          | 275                                          | 278                                          |

| 300.0                         | 171                                         | 195                                         | 203                                          | 205                                          | 207                                          | 209                                          | 211                                          | 213                                          |

| 200.0                         | 119                                         | 136                                         | 141                                          | 143                                          | 145                                          | 146                                          | 148                                          | 150                                          |

| 100.0                         | 70                                          | 79                                          | 82                                           | 84                                           | 85                                           | 87                                           | 88                                           | 89                                           |

| 50.0                          | 50                                          | 55                                          | 57                                           | 58                                           | 59                                           | 61                                           | 62                                           | 63                                           |

| 40.0                          | 47                                          | 51                                          | 53                                           | 54                                           | 55                                           | 56                                           | 57                                           | 58                                           |

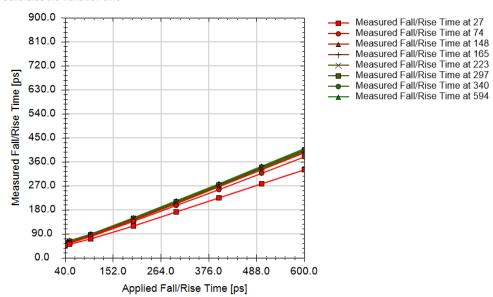

Figure 22 Example result for Fall/Rise Time Calibration

- Result: (Pass/Fail) Test is considered as passed if transition times are calibrated successfully.

- Set Fall/Rise Time [ps]: The applied transition time for this step.

- Measured Fall/Rise Time at xx MHz [ps]: Measured transition time for this step at a specific data rate.

## Sink Calibrations — HDMI 1.4

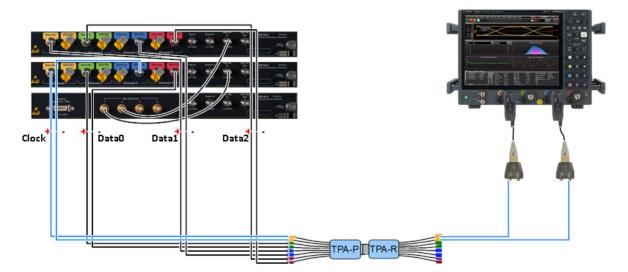

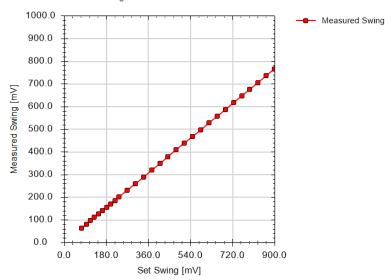

## Swing Calibration

## Availability

- HDMI 1.4

- · Clock+, Clock-, Data0+, Data0-, Data1+, Data1-, Data2+, Data2-

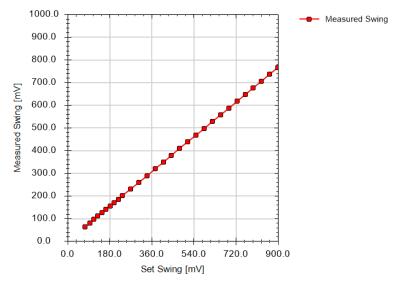

## Purpose and Method

The test fixtures and cables attenuate the data or clock signals. To compensate for this, the differential signal levels are calibrated by connecting an HDMI fixture to the HDMI setup and measuring the differential swing with a DSO.

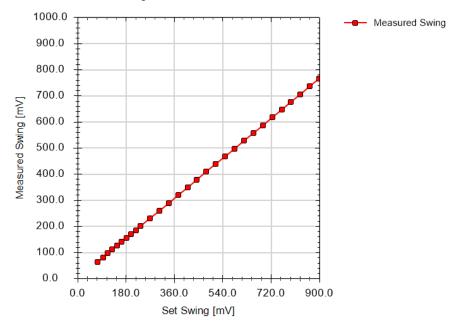

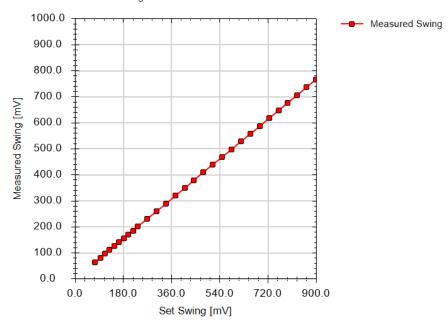

For the calibration, a software PRBS signal is generated at different swing voltage levels. For each step, the DSO measures the histogram to find the most frequently attained value of the differential swing. This calibration is done for each channel of the signal generator

## Connection Diagram

Figure 23 shows the connection diagram for the Swing Clock+ calibration. The differential probe head must be connected to the TPA-R output of the specific channel to be calibrated.

Figure 23 Example connection diagram for Sink Swing Calibration – M8195A setup

NOTE

This connection diagram is specifically for the N5444A/N28XXA probe head. If a different probe head is selected in the Configure DUT dialog, the connection diagram will be slightly different.

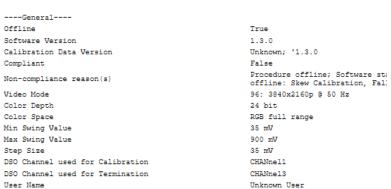

## Ck+ 64: 1920x1080p @ 100 Hz

## [Not Compliant]

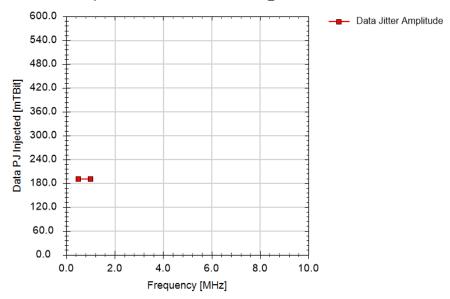

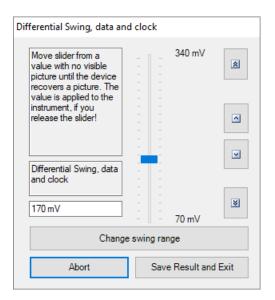

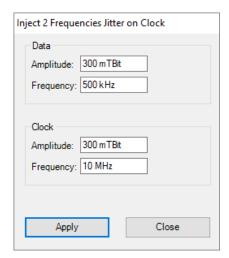

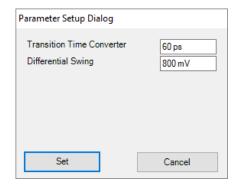

Calibrates the Generator Swing