Choose a country or area to see content specific to your location

您希望搜索哪方面的内容?

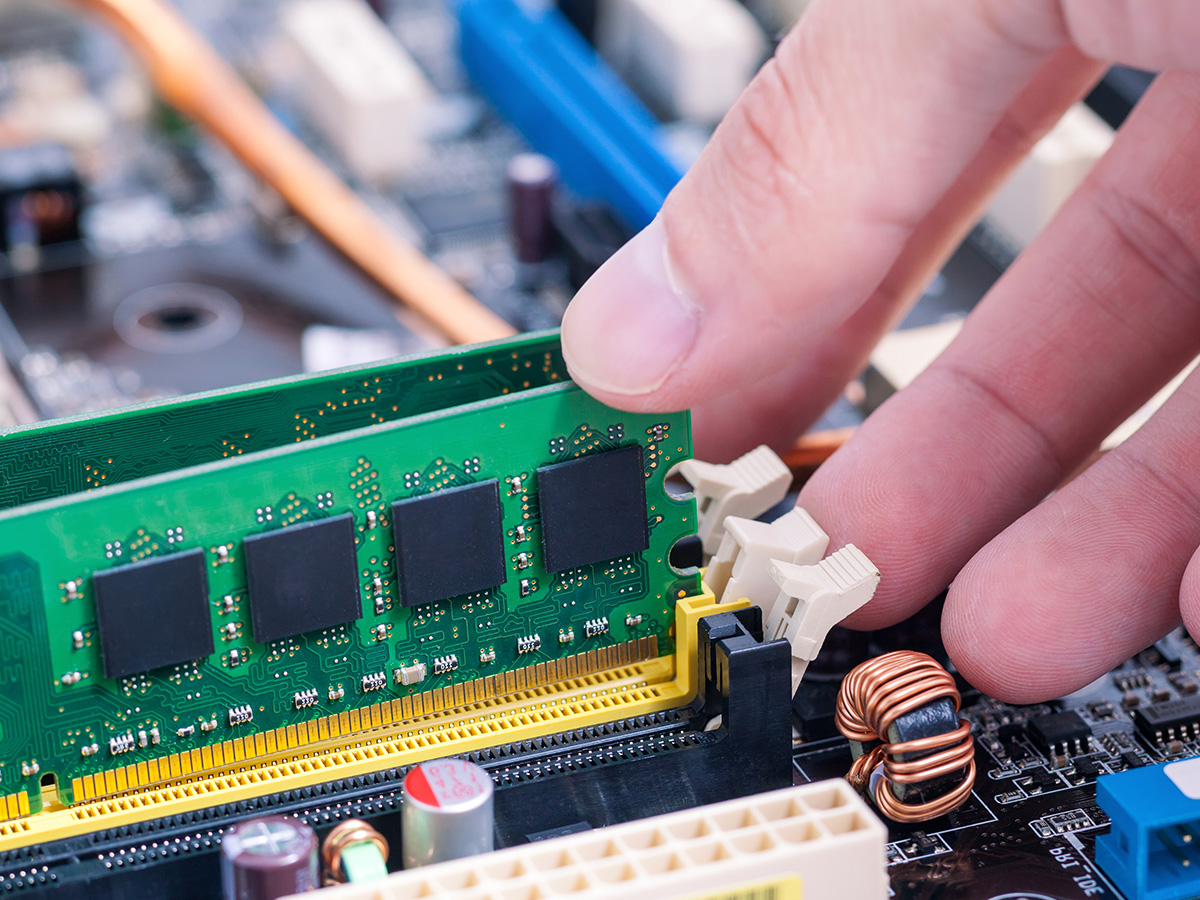

双倍数据速率DDR内存

无论对于芯片设计商还是器件制造商来说,DDR内存可谓是无处不在——除了在服务器、工作站和台式机中之外,还会内置在消费类电子产品、汽车和其他系统设计中。 每一代新的 DDR(双倍数据速率)SDRAM(同步动态随机内存)标准都会在许多方面带来显著改进,包括速度、尺寸和功率效率。 同样地,这些改进也会带来新的设计和测试挑战。 低功耗 DDR(LPDDR)专门用于移动设备,因而具有独特的测试挑战。 我们可以赋能您快速准确地测试 DDR内存设计中的所有必要参数,更快地把设计转化为产品推向市场。

双倍数据速率DDR内存设计和仿真

更快的网络速度需要有更快的内存与之配套。 每个新版本的 LPDDR / DDR 标准都会支持更快地存取内存中的数据。 DDR技术的速度越来越快,这也让您的设计和确认工作面临新的挑战。 设计和仿真 DDR内存系统有助于在硅片下线(silicon tapeout)之前提早发现问题,保障您的设计具备良好的信号完整性。 设计和仿真软件可用于优化您的发射机、接收机和信道设计,以便按照预期的速度级别实现最佳性能和可靠性。在您生产第一个原型产品之前,我们可以帮助您在早期设计阶段排除信号完整性问题,确保功率效率,以及满足苛刻的误差裕量要求。

相关产品

DDR物理层测试

为了确保符合行业规范以及与其他器件保持良好的互操作性,您需要对自己的 LPDDR / DDR发射机(Tx)和DDR接收机(Rx)设计进行测试。 每一代新标准都会对 DDR物理层测试提出新要求。 DDR 5.0 尤其如此,它需要执行完全不同于先前几代标准的、全新的接收机一致性测试。 通过与 DDR内存规范的制定者 JEDEC 协会(电子设备与工程联合委员会)密切合作,我们开发出了一系列测量方法,可以依据精确的行业标准进行测试。

我们可以帮助您按照最新的行业标准,快速准确地测试您的 DDR内存设计,这样您就可以专注于设计工作,而不必分心了解每一代新标准的细节和要求。

DDR协议验证

数据损坏是确认 LPDDR / DDR设计时的常见问题。 确定数据损坏的根源并非易事。 通常,在您的设计中不是有信号完整性问题,就是有功能问题。

当 DDR存储系统的表现不及预期时,您需要使用功能调试、分析和协议合规性验证解决方案,以便获得跟踪捕获和分析能力。 我们可以提供出色的洞察能力,帮您了解系统特性,快速找出问题根源。

双倍数据速率DDR内存更多资料

需要帮助或遇到问题?

京公网安备 11010502040140 号

京公网安备 11010502040140 号