What are you looking for?

What's New in High-Speed Digital Design and Simulation?

Watch the new demonstration videos below.

Keysight EDA 2024 for High-Speed Digital Design

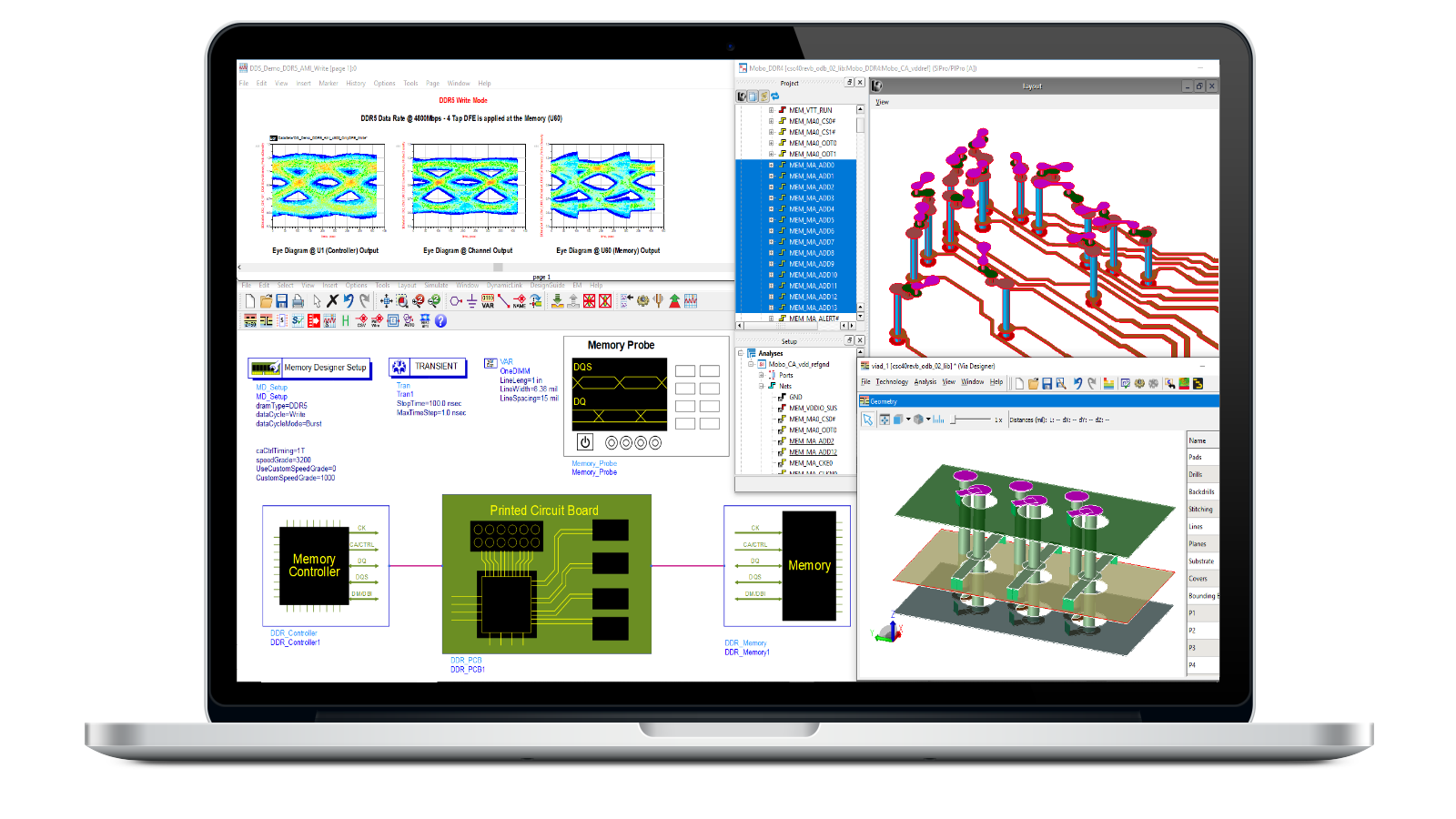

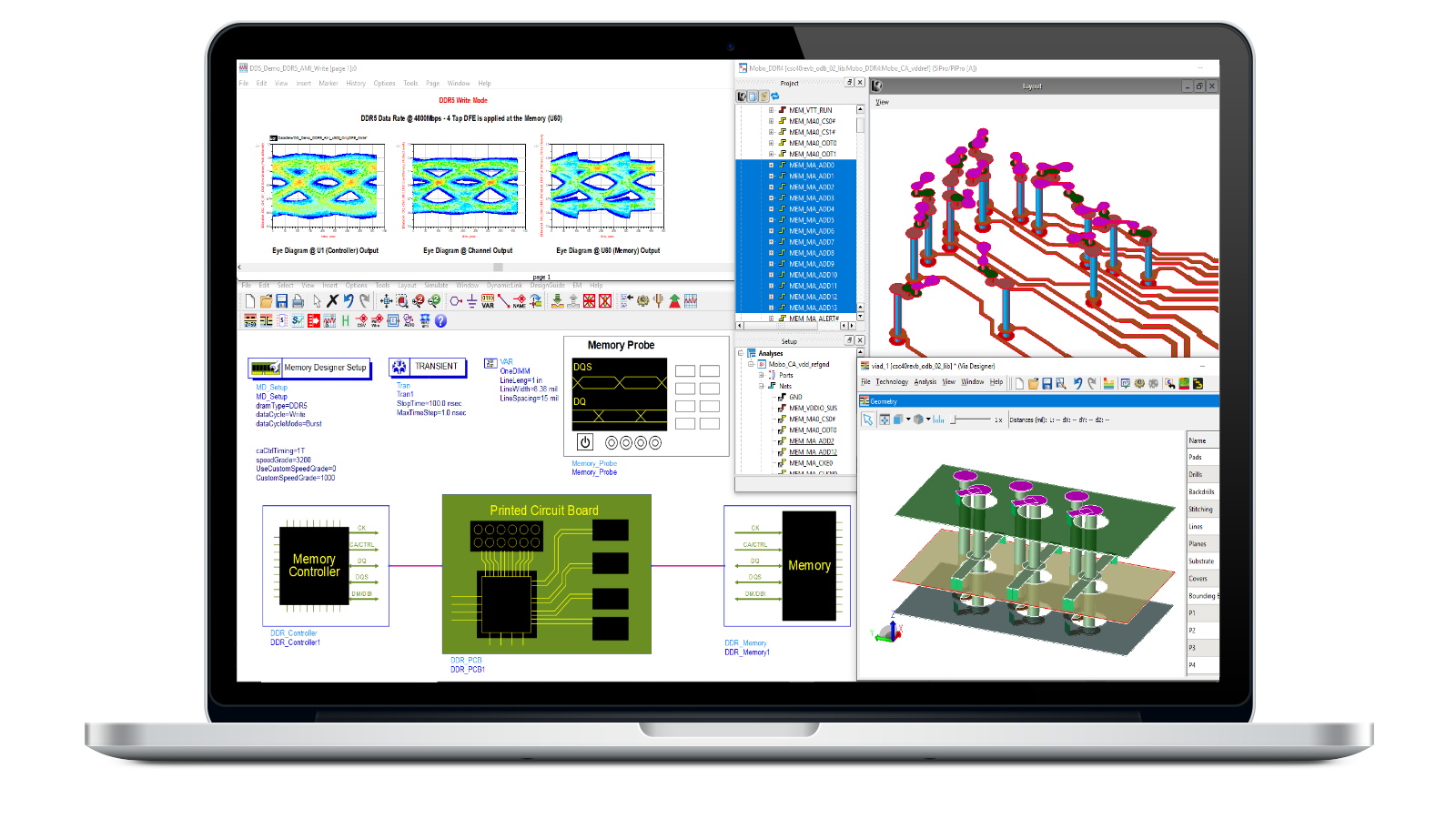

Keysight EDA 2024 includes the latest release of software for high-speed digital design. PathWave Advanced Design System (ADS) provides a powerful, integrated design and simulation environment to create digital twins and handle the complexities of today’s memory design and SerDes standards. The design environment helps you perform advanced measurements, run faster simulations, and gain critical insights to overcome signal integrity and power integrity challenges.

Highlights

Keysight EDA 2024 for High-Speed Digital design includes new and enhanced features and capabilities for the following application areas:

Learn more:

Custom Mask and Margin Calculation for PAM3 and NRZ

Memory Design

PathWave ADS Memory Designer minimizes your engineering efforts by utilizing smart design architecture and advanced workflows when setting up various memory interface simulations. It offers the most advanced simulation technologies, including 'forwarded clocking' solutions for jitter tracking and unmatched I/O conditions. New features include:

- Shape-driven custom mask margin and margin calculation support for NRZ and PAMn modulations

- Crosstalk limiter for speeding up simulation time while maintaining the simulation accuracy

- S-Parameter simulation within Memory Designer

- Genuine LPDDR5 compliance tests

- BER and Contour for Transient simulator

Learn More

Memory Design Demo Videos

Discover the most advanced workflow for memory systems using smart components, smart bus wires, and a streamlined workflow embedded in Memory Designer. Including new s-parameter simulation support and cross-talk limiter.

Learn how Keysight supports and helps leading-edge technology development by unlocking pathfinding mode for next generation memory systems. Are you working on pre-DDR6, LPDDR6, GDDR7, HBM4, or beyond? Newly introduced multi-level modulation and a new CA-to-CA ratio require simulator support not found in other EDA tools.

Explore a simulation-driven virtual compliance test workflow for DDR5 and LPDDR5 cases. Performing compliance tests at a much earlier design-stage, reduces risk and increases confidence in the design. The exact same tests that will be run on the first prototype.

Watch how the shape-based mask and mask margin calculations and how a comprehensive report can be generated in Memory Designer. Mask shapes have changed in recent generations of standards, learn how you can assure your design passes the mask spec and generate a comprehensive report.

SerDes Design

The PathWave ADS SerDes design solution offers a comprehensive design and simulation platform that effectively streamlines the SerDes design workflow, empowering designers to overcome challenges, reduce time-to-market, and refine design iterations. It covers various SerDes standards, including PCIe, USB, Ethernet, MIPI, and more. New features include:

- Design exploration and HTML report generation with Smart_Eye_Probe

- COM 3.9 and 4.0 support

- Retimer for PAM-n applications support

- IBIS 7.1 for AMI model generation support

Learn how PathWave ADS’s streamlined PCIe workflow helps designers to reduce time-to-market and reduce design spins. The speed of PCIe Gen6 is up to 64Gbps, with the adoption of PAM4 and now employs DFE with weighted sum of DFE tap limits.

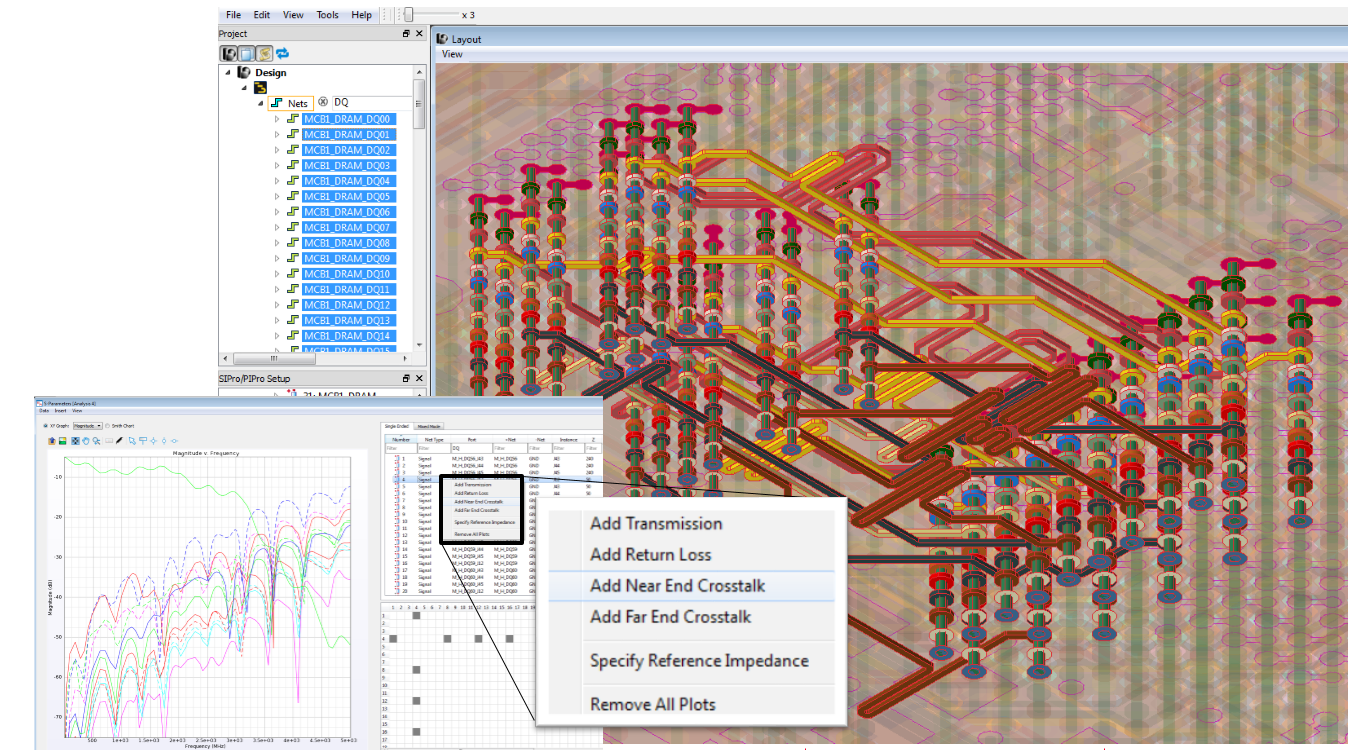

SIPro has a net-driven interface, that enables you to achieve layout to results in less than 20 clicks, delivering speed and accuracy.

Signal Integrity

PathWave ADS with SIPro EM for signal integrity provides a solution for analysis of complex high-speed PCBs, enabling you to characterize loss and coupling of signal nets, and ultimately extract an accurate EM model that can be used in the ADS transient and channel simulators. Highlight includes:

- SIPro (causality enforced) EM analysis

- Fast DDR analysis

- RapidScan Z0

Power Integrity

PathWave ADS with PIPro EM for power integrity provides an integrated engineering environment for end-to-end PI ecosystem simulations. Automation makes it easy to go from PCB EM simulations for DC IR Drop, AC Impedance, and conducted EMI to a digital twin schematic for post-layout optimization and hardware debugging. Highlights include:

- Explore conducted and radiated EMI for a dynamic switching regulator using the CISPR 25 standard setup

- Try out DC IR Drop with a cascade of regulators to investigate multiple power rails in one simulation

- Use AC EM models to optimize decoupling capacitors for high-power multiphase regulator PDNs and then investigate the results with an EMI analysis

Power delivery challenges continue to expand. Power Integrity engineers are learning more ways to simulate, optimize, and validate designs before expensive fabrication. This video will show you how to expand the basic Power Integrity workflow with DC, AC, and Transient simulation to include EMI.

Download the ADS workspace for this video:

This video demonstrates three ways to maximize your PCB design productivity.

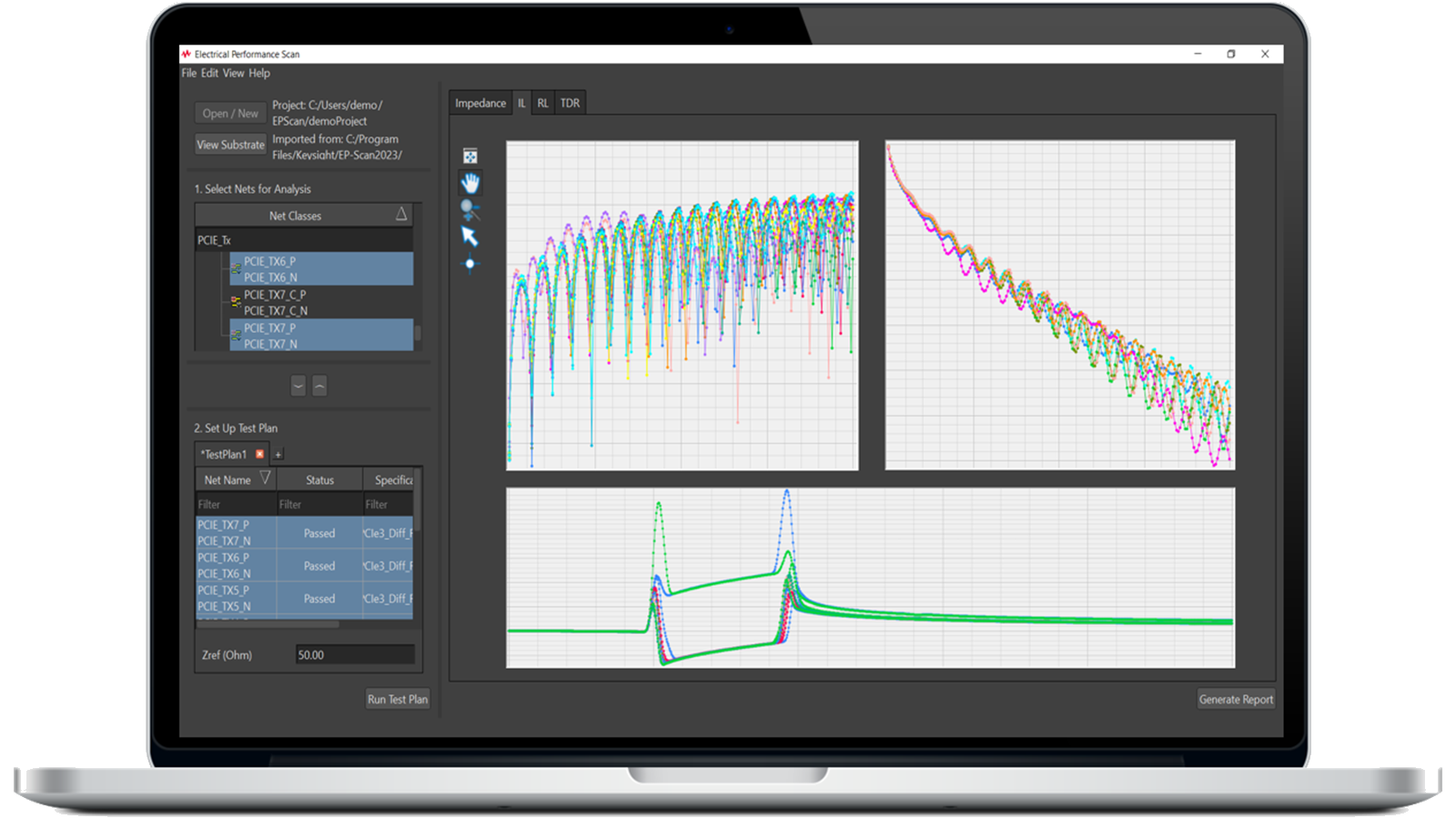

Electrical Performance Scan (EP-Scan)

The ultimate Signal Integrity tool for your hardware design

EP-Scan simplifies the comparison process between different versions of the printed circuit board design, making it easy to see and report performance differences. Highlights in EP-Scan 2024 inlcude:

- Eye diagram generation

- Net analysis with series components

- Layout view and impedance map

Learn More

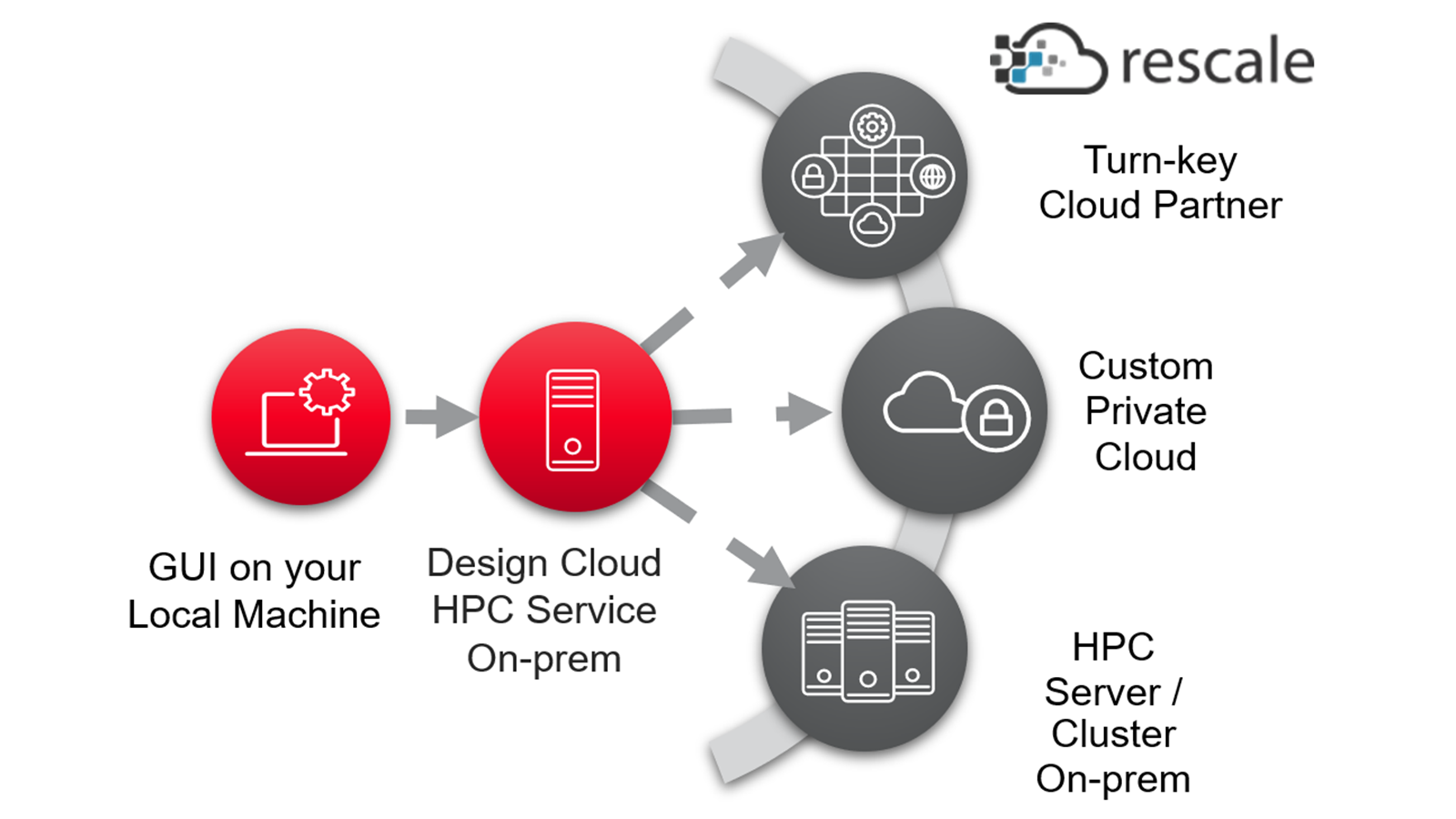

Design Cloud

Keysight Design Cloud is a new user-experience for cloud and high-performance computing (HPC), enabling you to simulate more and wait less. Highlights include:

- Cloud-based HPC for Memory Designer circuit and EM simulations provide parallel processing for an 80% reduction in simulation times.

- Keysight’s turn-key cloud partner, Rescale, enables you to easily launch unlimited cloud hardware in minutes.

Design Cloud for cloud-based high-performance computing

Keysight EDA Software for HSD Design

Featured Resources

Frequently Asked Questions

Electronic design is the process of creating, testing, and optimizing electronic circuits and systems. It can involve analog, digital, or mixed-signal components and technologies and applies to various domains, such as communications, data centers, and semiconductors.

EDA software is a computer-aided design category of tools for electronic circuits and systems. EDA software tools simulate the behavior and performance of electronic circuits and systems under various conditions and scenarios before fabrication or implementation. They perform different types of simulation, such as logic, functional, timing, electrical, thermal, and electromagnetic, helping designers reduce the risk of design errors, improve the quality of the final product, and save time and money in the development process.

High-speed digital design is a subset of electronic design that deals with the physical layer of digital circuits and communication systems operating at high data rates. It requires special attention to the effects of signal integrity, power integrity, electromagnetic interference, and thermal management. High-speed digital design can enable faster data transfer, lower power consumption, and higher performance in electronic systems.

Standards-driven design is an electronic design method that follows predefined specifications and protocols for communication, data exchange, and interoperability between different devices and systems. Standards-based design can facilitate compatibility, reliability, and scalability in electronic systems. Examples of standards-based design include USB, PCIe®, UCIe, and DDR.

Universal Serial Bus (USB) is a standard for communication and power delivery between devices and hosts, such as computers, smartphones, cameras, and peripherals. USB supports various data rates, from 1.5 Mbps (USB 1.0) to 80 Gbps (USB4 Version 2.0). USB also supports different power delivery modes, from 2.5 W (USB 2.0) to 240 W (USB PD 3.1). USB4 Version 2.0 is the latest version of the standard and is backward compatible with USB 3.2, USB 2.0, and Thunderbolt 3.

Peripheral Component Interconnect Express (PCIe) is a standard for high-speed serial communication between devices and hosts, such as computers, graphics cards, network cards, and storage devices. PCIe supports various data rates, from 2.5 GT/s (PCIe 1.0) to 64 GT/s (PCIe 6.0). The PCI Special Interest Group (PCI-SIG®) defines specifications and compliance tests that guarantee the interoperability of PCIe systems. PCIe also supports different lane configurations, from x1 to x32, to increase bandwidth and performance.

Universal Chiplet Interconnect Express (UCIe) is a standard for high-speed serial communication between chiplets. Designers can combine these small integrated circuits to form larger, more complex chips. UCIe is based on CXL / PCIe and supports the same data rates and lane configurations. UCIe enables chiplet-based designs that reduce cost, power consumption, and design complexity while increasing performance and scalability.

A chiplet is a small, modular chip that performs a specific function very well. For example, a chiplet can be a processor core, a memory block, an I/O driver, or a signal processing unit. Chiplets are designed to be used in a chiplet-based architecture, in which multiple chiplets are connected through a standardized high-speed digital interface, such as UCIe, to form a complete system-on-chip (SoC).

Double Data Rate (DDR) Synchronous Dynamic Random Access Memory (SDRAM) is a standard for high-speed memory communication between devices and hosts, such as computers, memory modules, and graphics cards. DDR supports various data rates, from 200 Mbps (DDR) to 6400 Mbps (DDR5). DDR also supports different memory capacities, from 64 MB (DDR) to 64 GB (DDR5). DDR transfers data on the clock signal's rising and falling edges, doubling the effective bandwidth.

See what you may have missed in the 2023 release.

Want help or have questions?

京公网安备 11010502040140 号

京公网安备 11010502040140 号